Hello TI expert

This is our first time to use DRV8705S-Q1 + 4 x N-mosfet as H-bridge. The N-mosfet is TQM056NH04LCR from TSC. I would like to double check some SPI registers.

1. DRV_CTRL1 & DRV_CTRL2

For TQM056NH04LCR, Qgd is 4.6 nC (Type) and 9.2 nC (Max). And for many mosfets, the rise and fall time 100ns to 300ns or more is acceptable. So IDRVN_HS and IDRVN_LS is selected as 24mA. (Type Slew Rate 4.6nC / 24mA = 192ns). But as we konw, for mosfet, the rise time is always less than fall time. So we would like to select 12mA as IDRVP_HS and IDRVP_LS.

I want to get your opinion on this configation for DRV_CTRL1 & DRV_CTRL2.

2. DRV_CTRL3

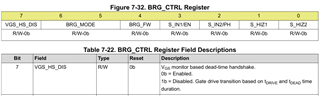

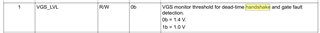

I know that we could use VGS_TDEAD to inset the configurated digital dead-time. But in BRG_CTRL, we have setted the VGS_HS_DIS is enabled. So do we even need to set VGS_TDEAD or we could just set VGS_TDEAD to 0ns? Now DRV8705 has VGS_HS_DIS, what is point of configuring the VGS_TDEAD?

And for VGS_TDRV, we keep the default value (4us). Is it OK? And I want to know what condition need to change this VGS_TDRV value.

Thank you for your support!