Hi Team,

The spindle coil data (0x8324) can now be controlled by using 10M SPI data rate in the DSP STM C6678 (1G) IC single core master and the spindle motor can function.

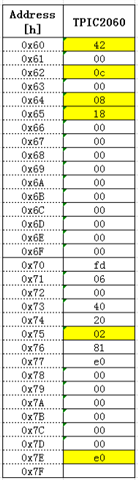

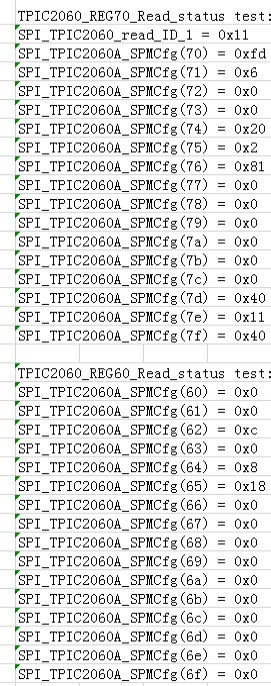

According to the IC specification, BIT0 bit FG signal.Spindle rotaion *** for speed monitor in REG7F. With 0x8324 data control, the FG signal is at an oscilloscope frequency of 2.9684 kHz (336us) and the REG7F read by the DSP main program is continuously changing.

1) Can the speed of the spindle be controlled by reading the frequency of FG change of REG7F?

2) The DSP chip operates at 1 GHz, which theoretically runs at 1 ns, plus an 8-bit transfer read of SPI (10M). ・・・ (8+2)・100ns=1us. Theoretically read 336/(1*2) = 168 high or 168 low. FG(BIT0) of REG7 read in emulated state is continuously tripping. Could you help check are these calculations correct?

Could you help check this case? Thanks.

Best Regards,

Cherry