Other Parts Discussed in Thread: DRV8955

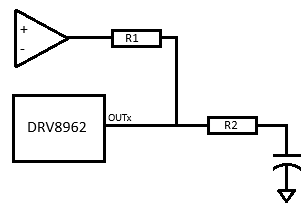

Hi. We have a non-typical application that drives a capacitive load using the DRV8962 and a power op-amp. The DRV8962 output and the op-amp output are connected in parallel to the capacitive load, with a resistor in between the DRV8962 and op-amp. See picture below for general connection.

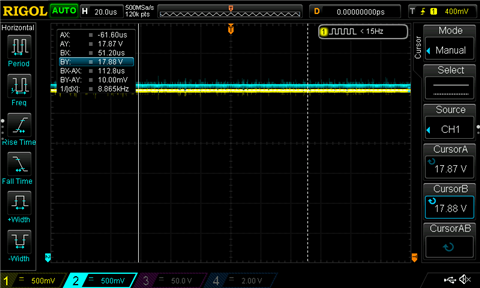

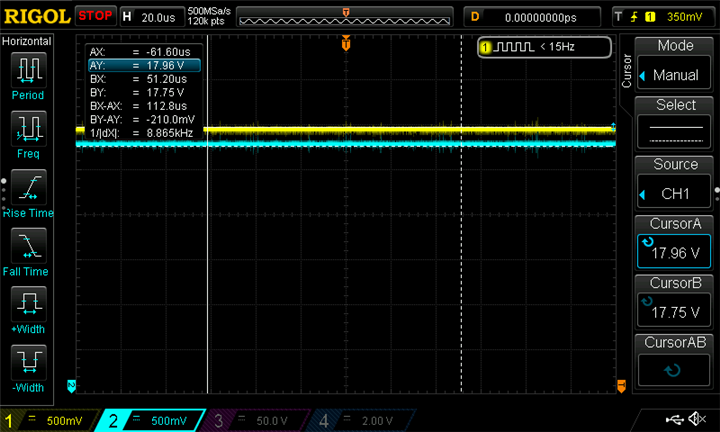

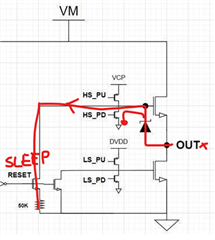

In general this setup is working fine. The op-amp controls the majority of the output signal to the capacitive load while the DRV8962 fires a high or low FET at certain signal transitions. When the capacitive load is held at a steady state voltage, the DRV8962 will be disabled (ENx low) and the op-amp holds the output voltage. The problem we are having is that in this state we are seeing about a 0.2V to 0.5V drop on R1. This is causing unnecessary heat dissipation on both R1 and the op-amp. As the capacitor is fully charged at this point, the only avenue for a resistive load would be the DRV8962 in its hi-Z state.

Additionally, if we put the DRV8962 in sleep mode, driving nSLEEP low, the resistive load is eliminated and there is no voltage drop on R1. Excessive heat is eliminated.

The relationship between the steady state voltage and voltage drop on R1 isn't as linear as I would expect so we are having some trouble determining the resistive load of the DRV8962. Do you have any details on the behavior/impedance of the DRV8962 OUT signals while disabled? We were not able to find any details in the datasheet. Thanks.