Hi team,

Customer is doing software eval of DRV8718, and below is the command

Write 87 to 0X07 (IC_CTRL1)

Write 12 to 0X08 (IC_CTRL2)

Write 12 to 0x26 (CSA_CTRL1)

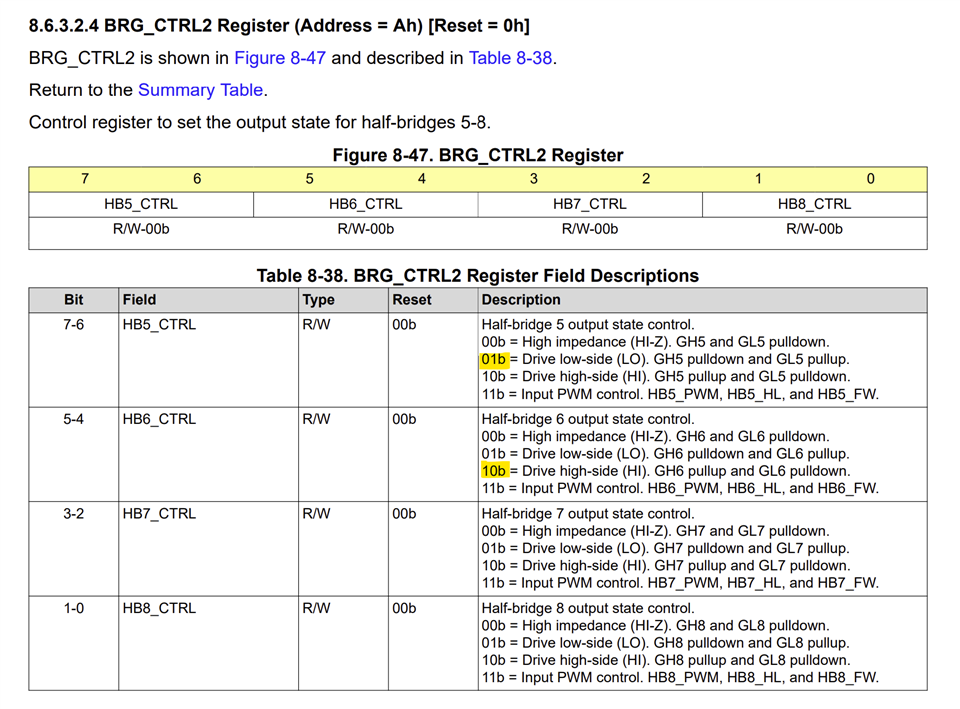

Write 00 to 0X09 (BRG_CTRL1)

Write 00 to 0X0A (BRG_CTRL2)

Then they connect half bridge 5 and 6 with a 1 ohm power resistor to simulate the motor load, enable the bridge by write 60 to 0X0A, there's no voltage change. Is there any step missing?

Thank you

Scarlett