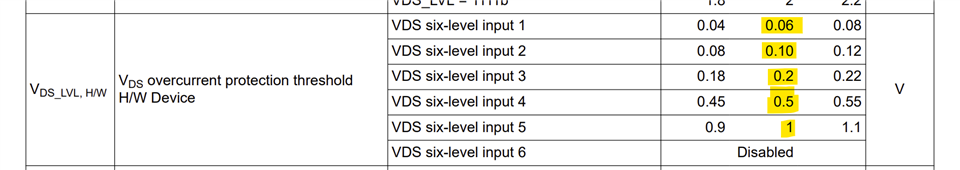

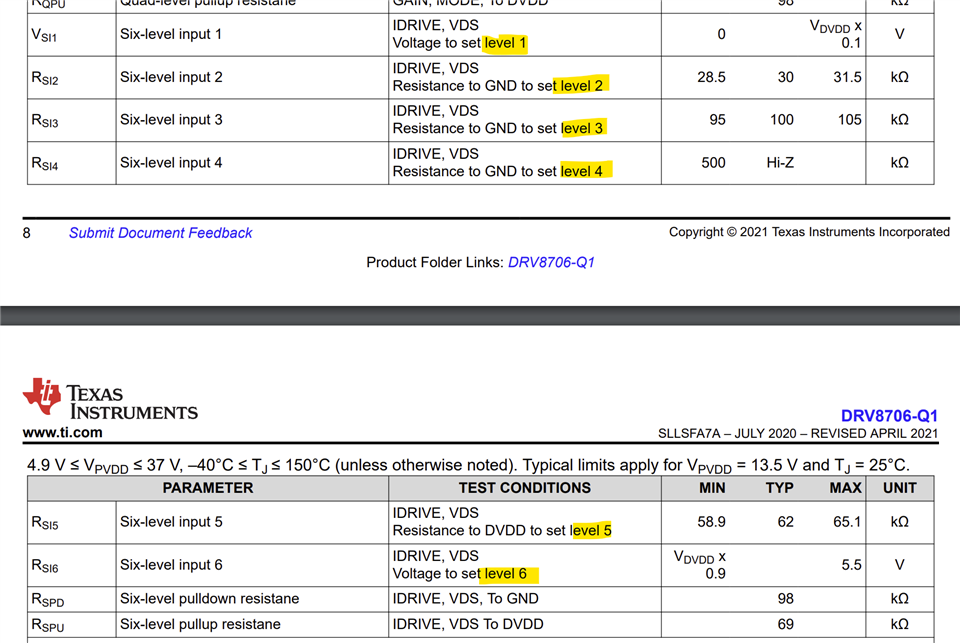

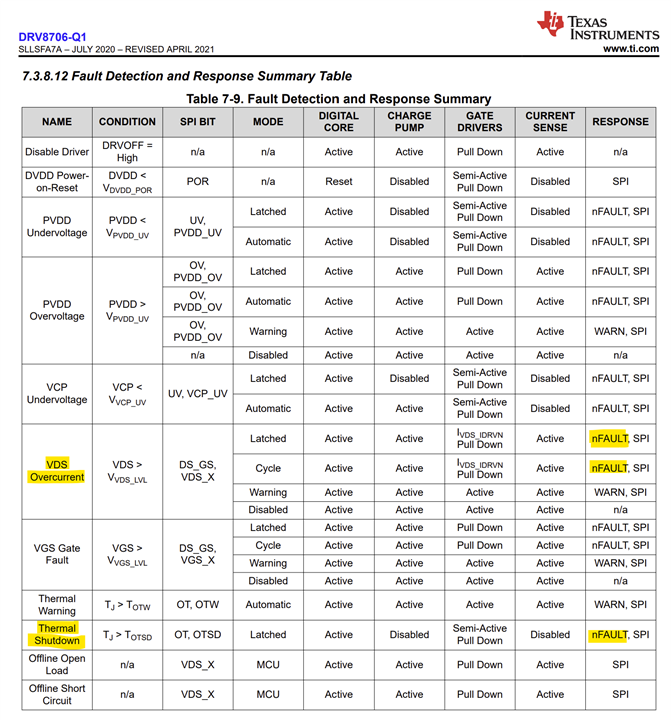

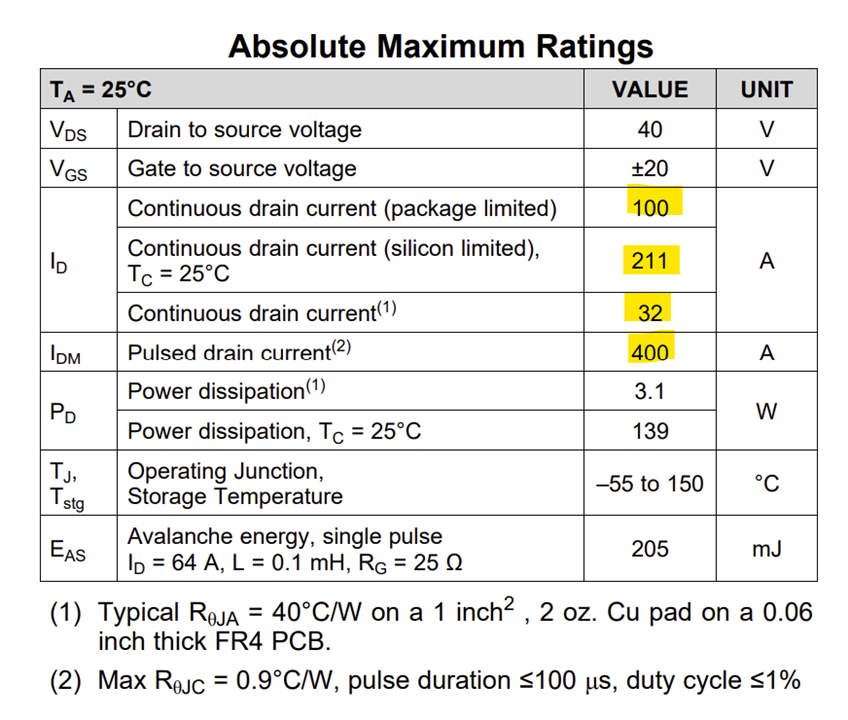

I am using the hardware version of this chip. I have a board built and successfully running brushed motors. I did my calculations for the various control resistors based on 100A max. I currently have the overcurrent protection disabled (pin 4 VDS tied to DVDD) because I couldn't figure out how to set the resistor divider to feed the overcurrent control pin 4. I couldn't make out what the Level 1-5 meant in terms of max current.

Can someone please advise?

Ideally, I want to set it to kick in around 70 or 80A. But I still want to understand what each level would represent if the calculations were based on 100A.

Sincerely,

Craig Kessler

AndyMark, Inc.