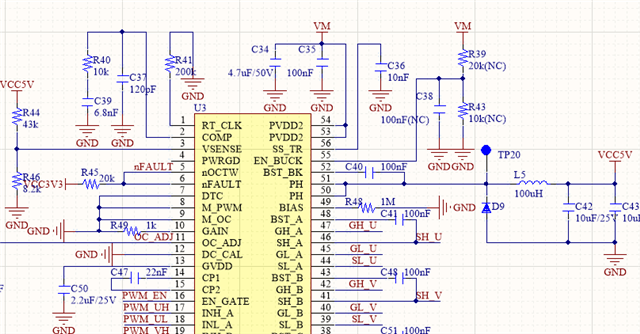

Other Parts Discussed in Thread: DRV8328

Hi Team,

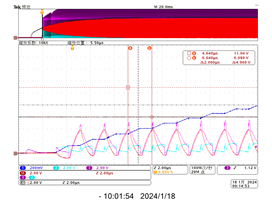

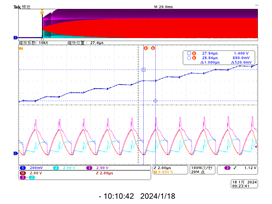

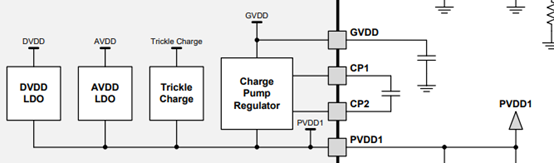

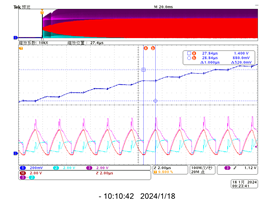

The test condition is 24V, and the waveform collected during the test is shown in the figure below. The amplification part is the GVDD startup stage. CH1 is the GVDD waveform, CH2 is the CP1 terminal, and CH3 is the CP2 terminal. Is the voltage increase of GVDD due to the charge and discharge of the CP capacitor? The customer considers that the reference voltages of the two are different, and he wants to know how to increase the voltage? Could you share and explain the working mode of Charge pump and GVDD?

Regards,

Annie