Other Parts Discussed in Thread: DRV8462,

Hi,

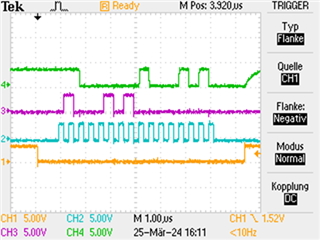

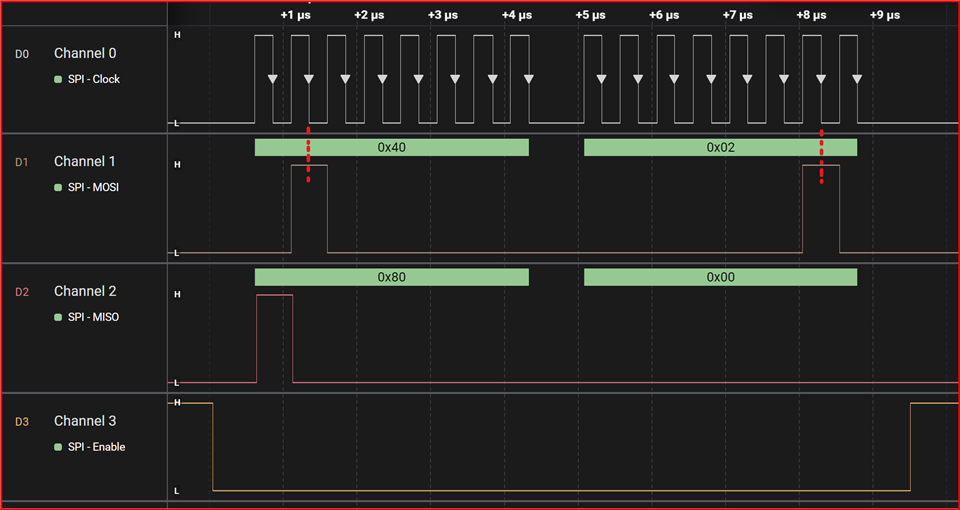

the DRV8462EVM works with the GUI, but when I try to control the DRV8462 with an external MCU it doesn't work.

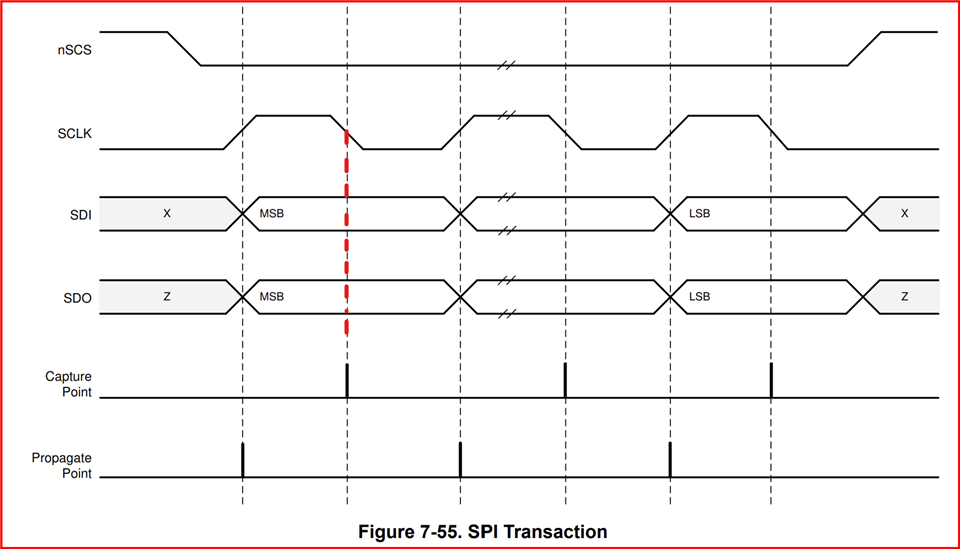

When I send 0x4500 on the SDI to the DRV8462, 0xE045 comes back on the SDO. But 0xExxx means that the UVLO bit is set.

But I have 24VDC on the VM terminal and the 3.3V comes from the external board. Booth LED for Vin an 3V3 are on and there are 5V on the DVDD pin.

What could be wrong?