Hi Team,

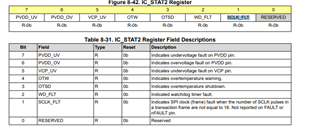

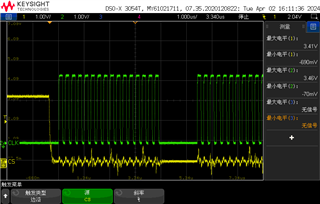

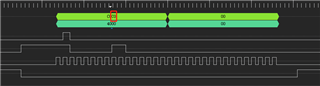

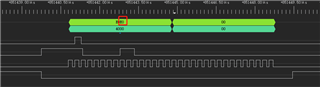

The DRV8714 SPI clock should be 16bit. While we sent 32bit clock in one nSCS, will this trigger the SPI clock fault?

During the test we didn't received the SPI clock fault indication.

May I know what is the definition of the 'Invalid SPI Lock Frame' ?

Thanks!

Best,

Frank