Hi, all

We are working on the project using drv8308.

I'm testing the board I designed.

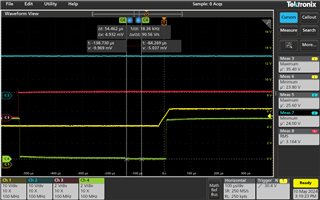

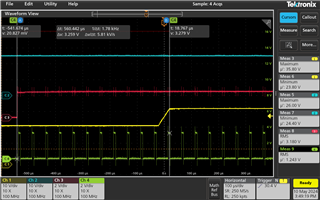

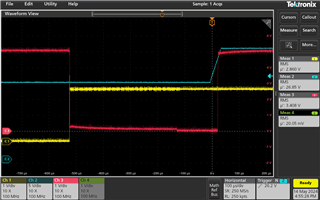

The motor works well, but reading the motor register confirms the CP fault.

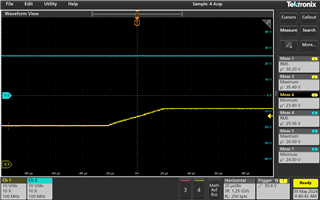

1uf-25V capacitor between VCP (28) and VM (27)

Does changing the capacitor to 1uf-50V fix the problem?

I'd like to try changing that capacitor, but I don't have 1uf-50V.

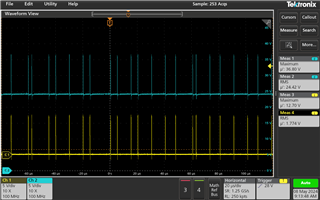

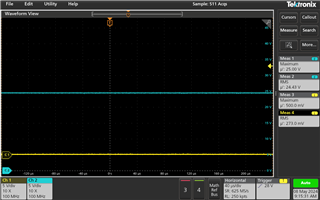

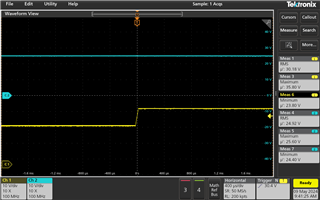

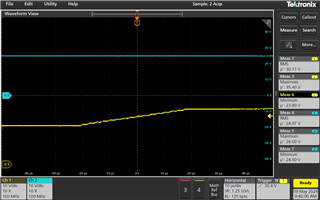

When the VCP voltage is measured, 34.4V is measured.

Is there a way to fix the CP failure?