Hello Team,

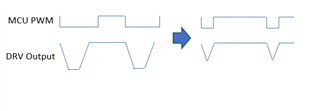

what would be the resolution of the PWM between 90% and 100%?

Is there a restriction on minium off-time in our gate drivers?

We know that some architecture when achieving 90% duty cycle they skip directly to 100% but this in some application critical.

So, do we have more description about the behavior between 90% and 100% duty cycle for DRV8702?

Many Thanks

Josef