Tool/software:

Hi Team,

I have several questions for DRV8243-Q1 (S) below:

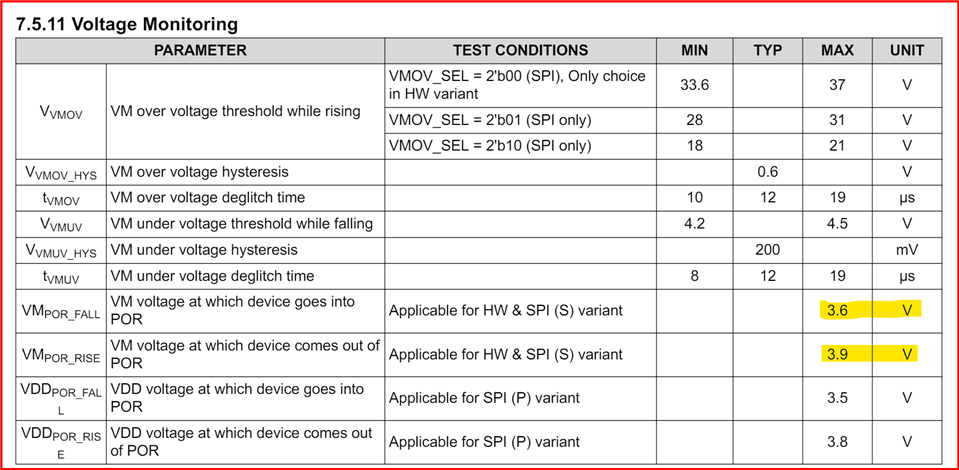

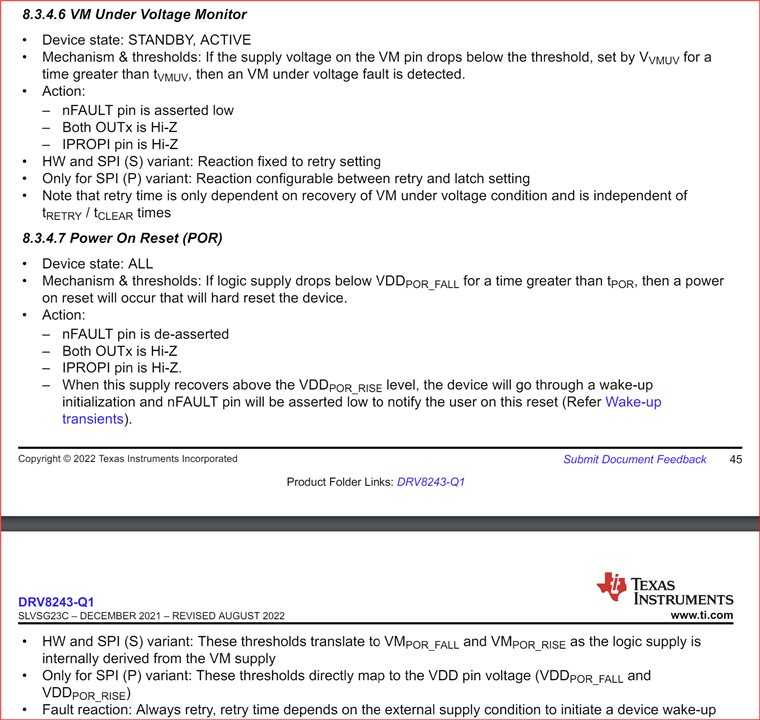

- From datasheet, when VM drops below VMPOR_FALL, all register will reset. But what's the deglitch time for VMPOR_FALL?

- When reset happened by VM drops < VMPOR_FALL, the out1 & out2 will also be reset. But does out change from Normal out to reset out directly, or out1/2 may has uncertain state during all registers is being reset?

Thank you!

Marc