Tool/software:

Dear BLDC team,

Regarding nFAULT of DRV8353HRTAT:

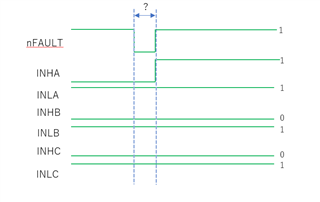

If the VVDS_OCP threshold in MOSFETVDS Overcurrent Protection (VDS_OCP) is exceeded for a duration longer than the tOCP_DEG deglitch time, the VDS_OCP event is recognized, and nFAULT goes low.

When nFAULT is low, it is expected that if a new rising edge of the PWM input is applied, the VDS_OCP event will be cleared, and nFAULT will go high.

Your question is, when nFAULT is low and you want to clear the VDS_OCP event, how long should elapse after nFAULT goes low before inputting a new rising edge of the PWM input?

I have attached an image. The MODE is [3x PWM] MODE.

Best regards,

Tatsuya Ichikawa