Tool/software:

Hi team,

I have a few questions about DRV8705-Q1:

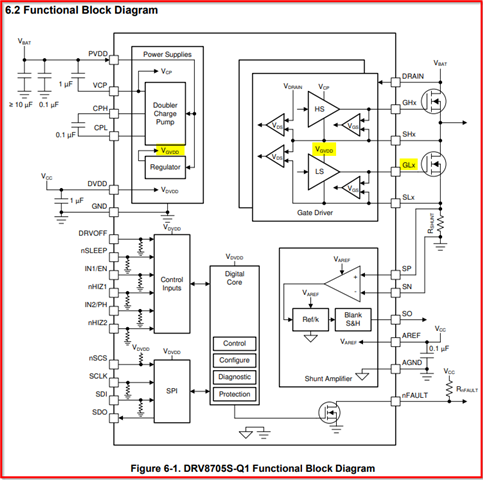

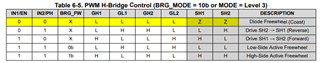

I use the DRV8705-Q1 in hardware mode, as a set of bridge drive outputs

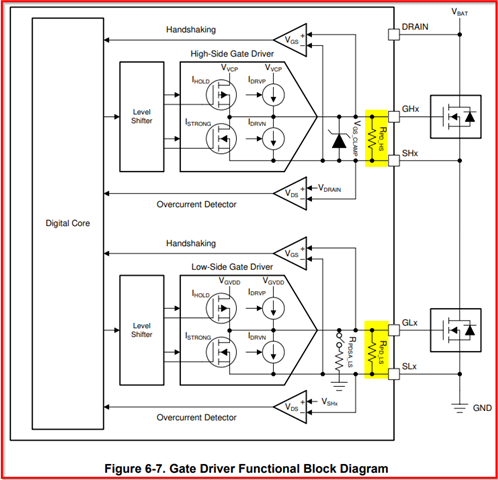

1.The GHx of the high-side switch is powered by the GLx by raising the voltage through a charge pump,Then, when the high-side switch is not turned on, who provides the electricity for the high-side switch GLx?

2.What is the voltage of GHx and GLx when the high side switch is not driven? Why?

3.When a short power failure occurs on the high side and a short power failure occurs on the low side, the chip will shut down the output due to VDS overcurrent detection. However, since the VDS overcurrent mode is fixed to cycle by cycle on the hardware device model, the fault bit will be cleared and the output will be retried, resulting in a negative pressure of -10V on SHx. Can this negative pressure chip withstand it?

4.In response to problem 3, I added the strategy of detecting that the nFAULT is low, judging that the chip is faulty, and then turning off the output. The program is refreshed every 100ms. Before the output is turned off by the software, I can see that the nFAULT pin of the chip constantly changes between high and low, which is not a stable state. The chip is still resetting nFAULT, is this strategy OK?

5.In cycle by cycle mode, after detecting an overcurrent event, the nFAULT will be set and the next PWM input will clear the nFAULT register bit, but I found in the actual test that the PWM has not input the nFAULT register bit is cleared, what is the reason?(The blue line is the high side switch output short ground, and the pink line is the nFAULT pin)

Hope to receive your reply, thank you~