Tool/software:

Hi team

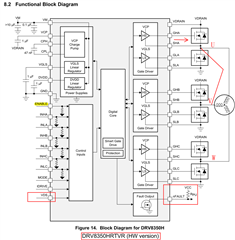

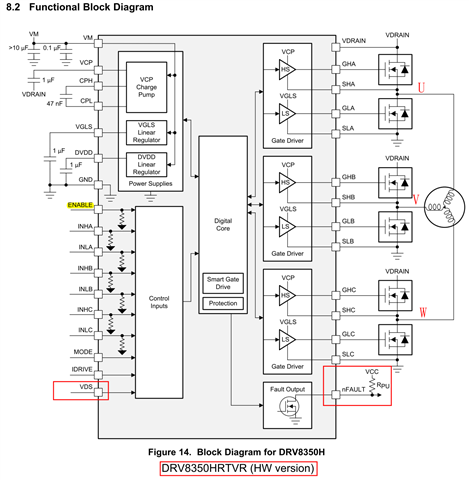

I use Device : DRV8350HRTVR (HW version)

Some question below

1. Does VDS protection detection protect "all six-arm" MOSFET?

2. The protection set by this VDS pin. Is it suitable for "all six-arm" MOSFET?

3. When overcurrent is triggered, will "all input" PWM signals(INHA~C & INLA~C) turned off?

Or only the arm of the overcurrent MOSFET (EX INHA)?

4. When overcurrent is triggered, nFault H-->L,how long will nFault to recover to H? (If INHA~C & INLA~C signals continues input)

Thanks~