Tool/software:

Hello Experts,

My customer has question as follows. Would you answer them, please?

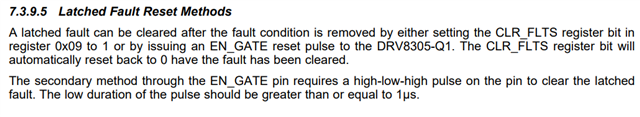

1. Recover from latched fault condition.

The latched fault condition will be indicated to the nFAULT-pin. To recover latched fault condition, customer need to write the CLR_FLTs bit asserted in register 0x9, bit D1. At this time, nFAULT-pin and gate driver are recovered to normal condition if latched fault condition is removed?

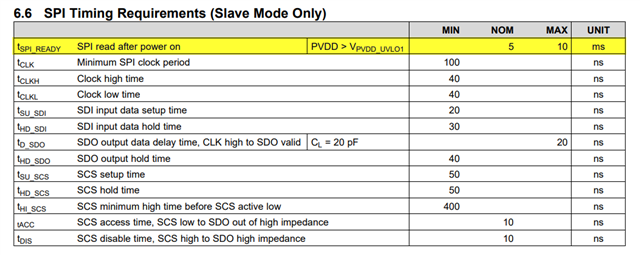

2. Power up sequence

When PVDD voltage is less than UVLO2, SPI communication is disabled, correct? Or If PVDD voltage is UVLO1<PVDD<UVLO2, SPI communication is still enabled?

3. PVDD_UVLO2

When device detect PVDD_UVLO2, Register 0x1(fault bit) and Register 0x3(bit 10) will be asserted, correct?

Best Regards,

Fujiwara