Other Parts Discussed in Thread: DRV8243-Q1

Tool/software:

Hi,

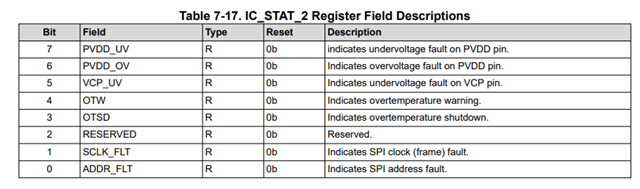

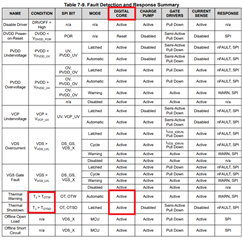

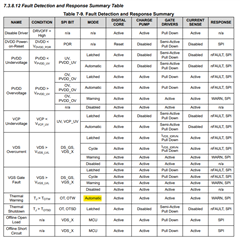

with the SPI-Version of the DRV8706-Q1, what is the Fault Reset Behaviour of the OTW and OTSD Bits?

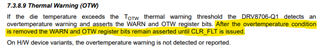

In the Datasheet p.34 it is stated that Both Bits are latched, on p.36 it is stated that the OTW clears automatically.

What is the Behaviour of the OTW and OTSD Bits?

For my Application I would need the current State of the Overtemperature Warning (thus it is set if it is over the Limit, and clear if it is under the Limit (including Hysterisis of course)). Is there any way to read this State without Continouously clearing all Errors using CLR_FLT?

Thanks for your Help,

Frederic Emmerth

Datasheet: