Tool/software:

Hi,

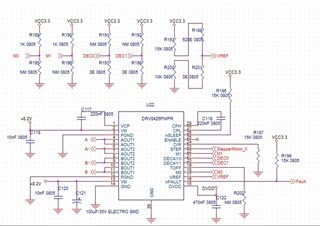

Please find the below schematic for DRV8426

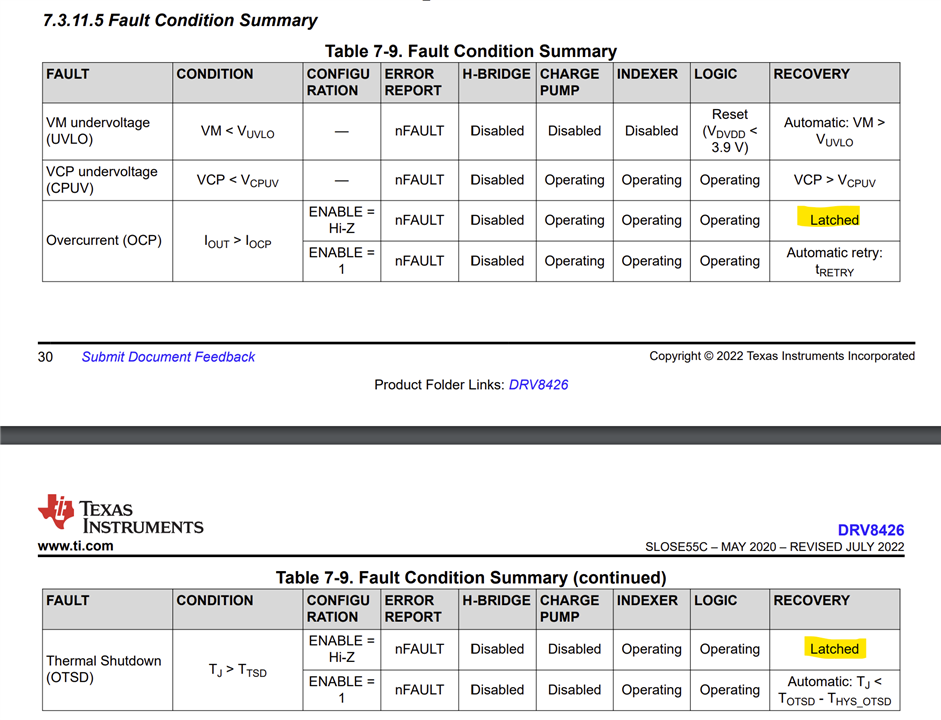

sometimes, during power recycle it gets trapped in improper condition,

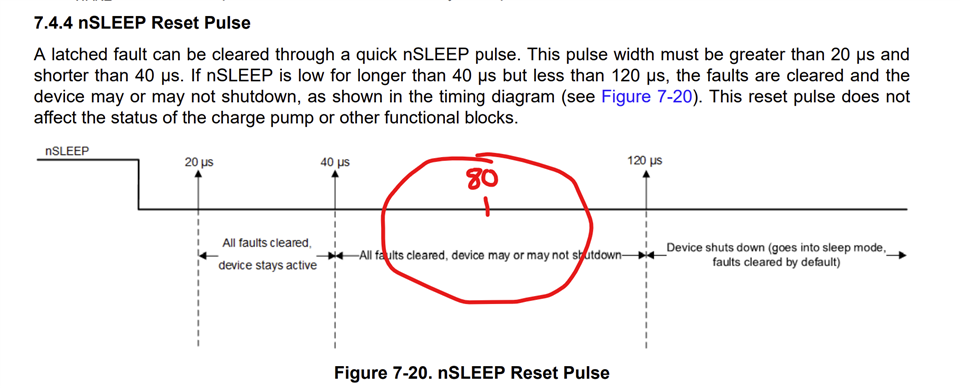

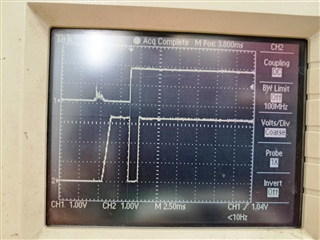

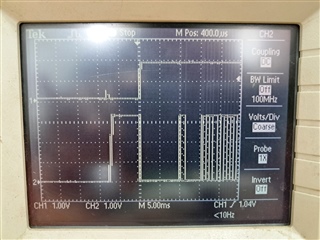

where we can observe toggling in "fault" pin & similar activity can be observed on winding output pins (on very few instances, it get recover from this situation, without any intervention----by sending low signal on enable/ nSLEEP pin )

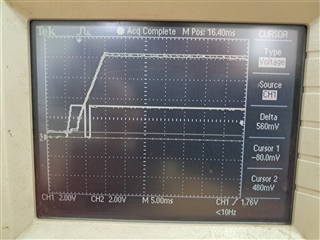

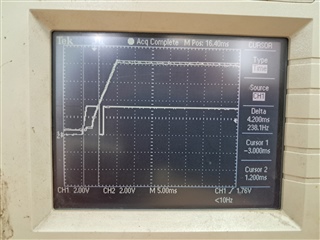

below are the images for enable pin & fault pin (in normal & problematic condition)

apart from above, it works fine in 1/8 mode

what can be root cause & recommended solution for it,

Regards,