Tool/software:

Dear TI Support Team,

I am working with the DRV8353RS gate driver and encountering difficulties with the SPI register read operation. The SPI write functions appear to be working correctly, but I am unable to read back valid data from the registers.

I have referred to Section 8.5.1.1.1 in the datasheet, particularly regarding the SDI input and SDO output word formats for SPI communication. For the read command:

I am setting the Read/Write bit (B15) to 1 to initiate the read.

The Address (A3–A0, bits B14–B11) is being set correctly, and I expect the data corresponding to the register to be returned in bits B10–B0 of the response.

However, in practice, the MISO line (Channel 0 in the attached logic analyzer capture) consistently returns 0xFF, rather than the expected register values. The MOSI signal (Channel 1) shows that the correct command (e.g., 0x90 for register read) is being sent, and the SPI clock and enable signals (Channels 2 and 3) are operating as required.

I have tried writing 0x00 content to 0x40 register rather than 0xFF, which is also not working as expeted.

Additionally, based on the datasheet, I understand that the first 5 bits of the response on the MISO line are "don't care" bits, but the following 11 bits (B10–B0) should contain the actual data from the register. This expected behavior is not occurring, and I am unsure what could be causing this mismatch.

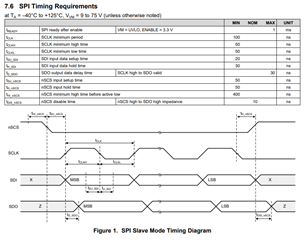

Could you kindly provide guidance on any potential issues that could cause the SPI read operation to fail in this way? Any specific timing requirements or other configuration settings that might resolve this would be greatly appreciated.

Thank you for your support!

Best regards,

- Himavanth Reddy