Other Parts Discussed in Thread: MSPM0G3507,

Tool/software:

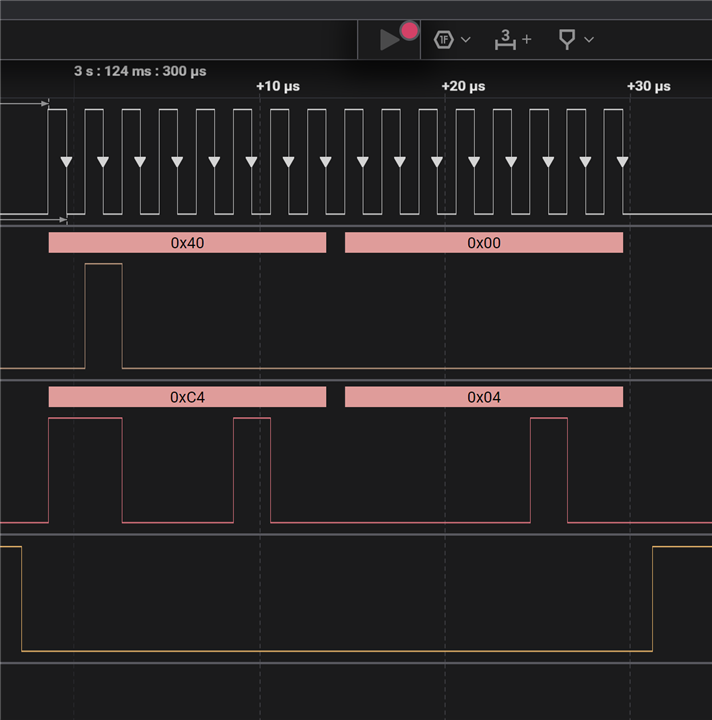

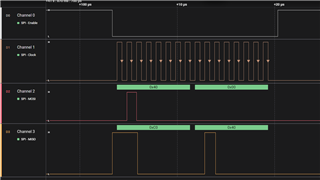

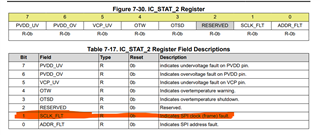

Hello, I’m working on a DRV8706 with an MSPM0G3507. I can read and write registers, but I'm consistently getting a fault status on the SPI.

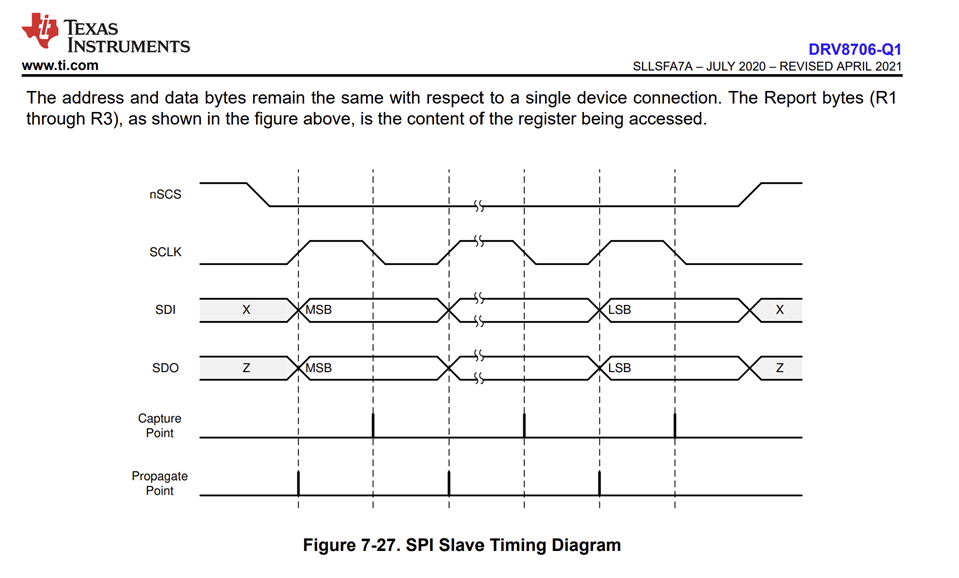

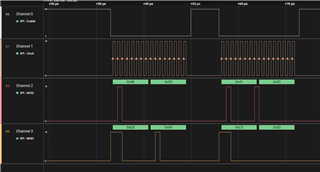

I've configured my SPI to 1MHz, with Polarity Low, Phase High, and No Parity. I have a timing diagram that seems coherent, but I’m not sure why I’m receiving this status.

Do you have any ideas or suggestions for me to test? Thank you in advance !