Tool/software:

Dear technical team,

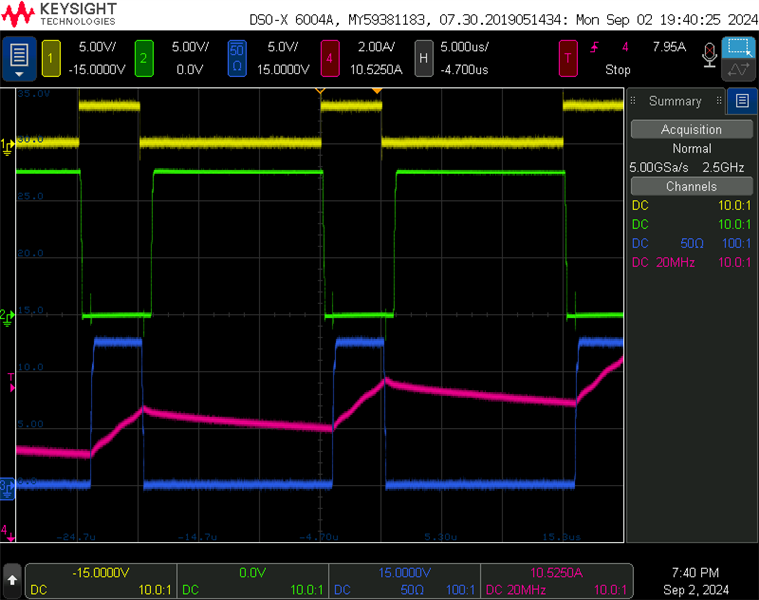

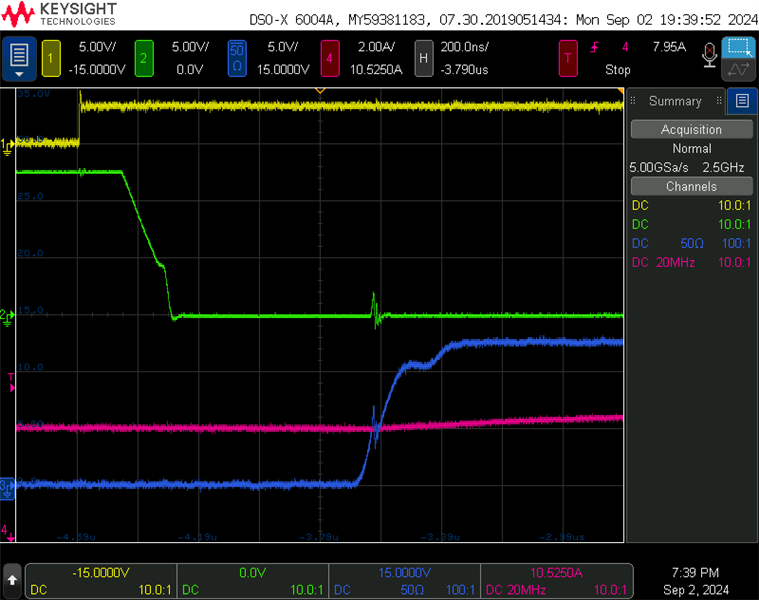

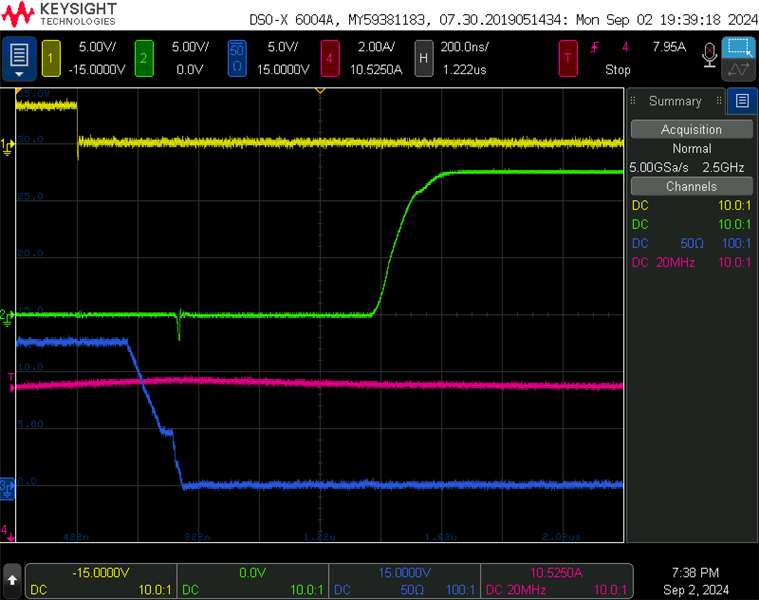

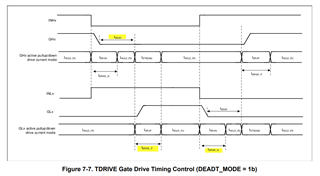

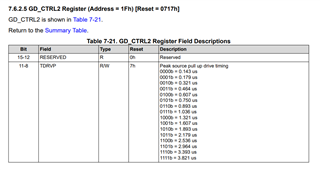

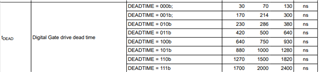

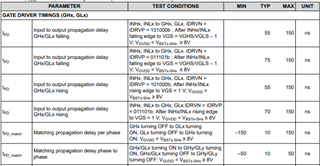

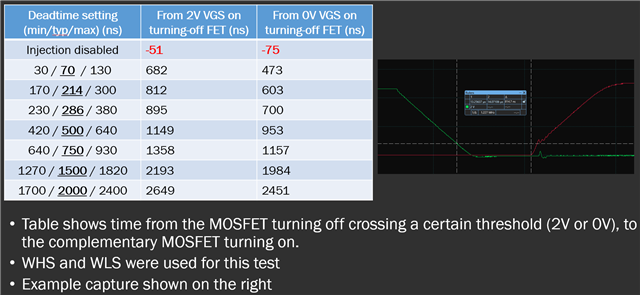

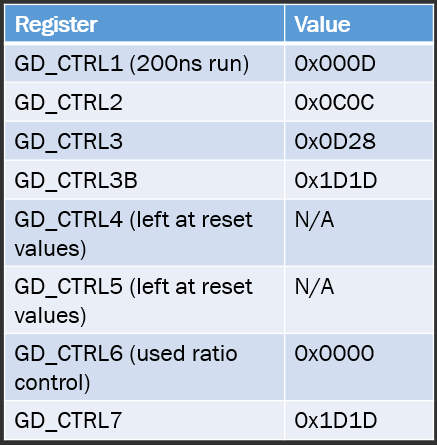

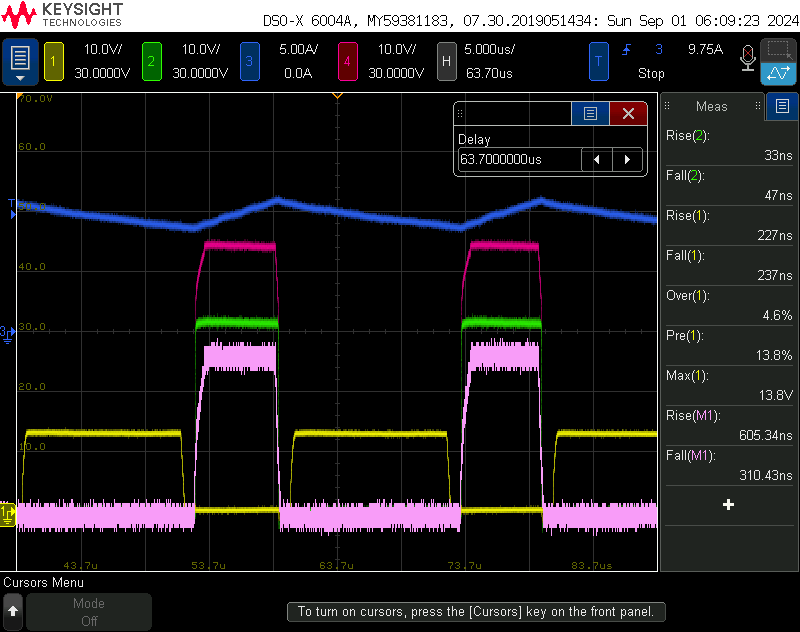

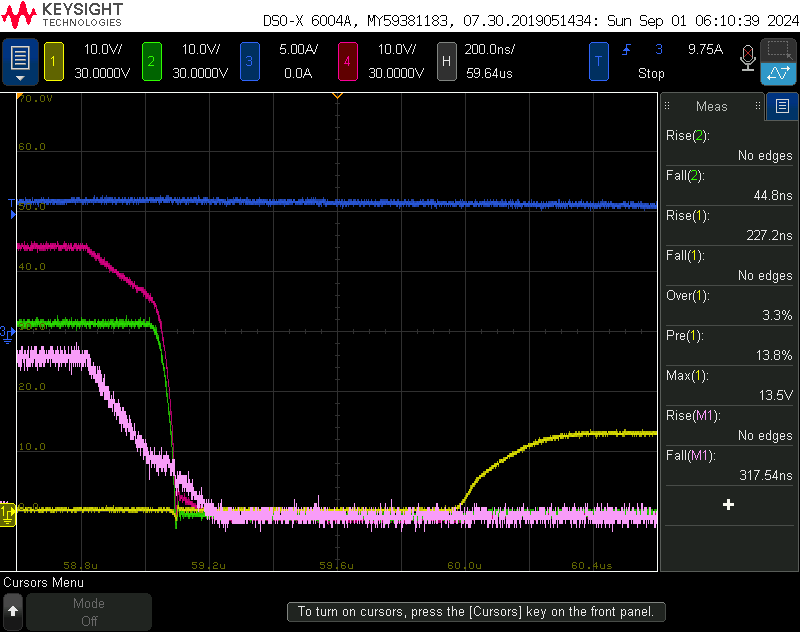

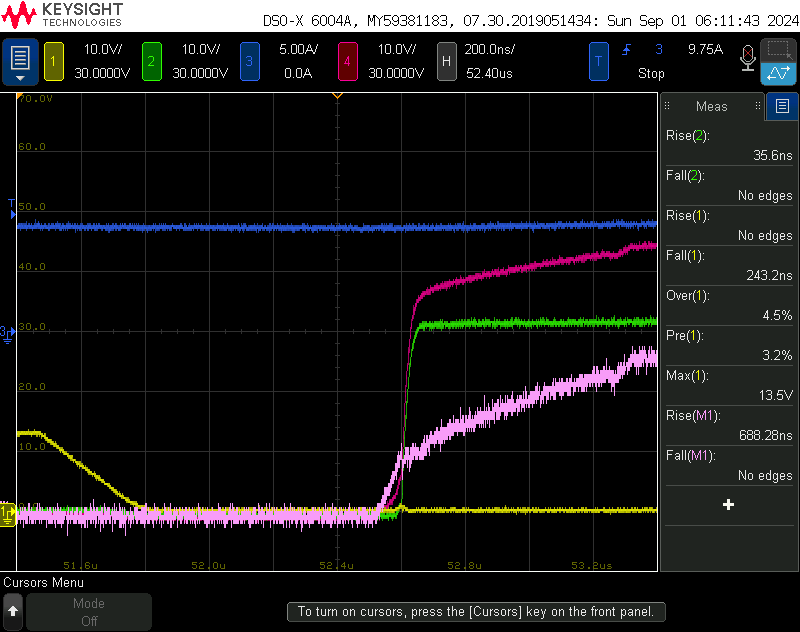

I'm optimizing the settings for my design and noticed the dead time is much higher than expected. I use DEADT_MODE = 1 (Dead time is inserted by monitoring gate driver outputs (GHx or GLx)) and DEADT = 001b (214 ns).

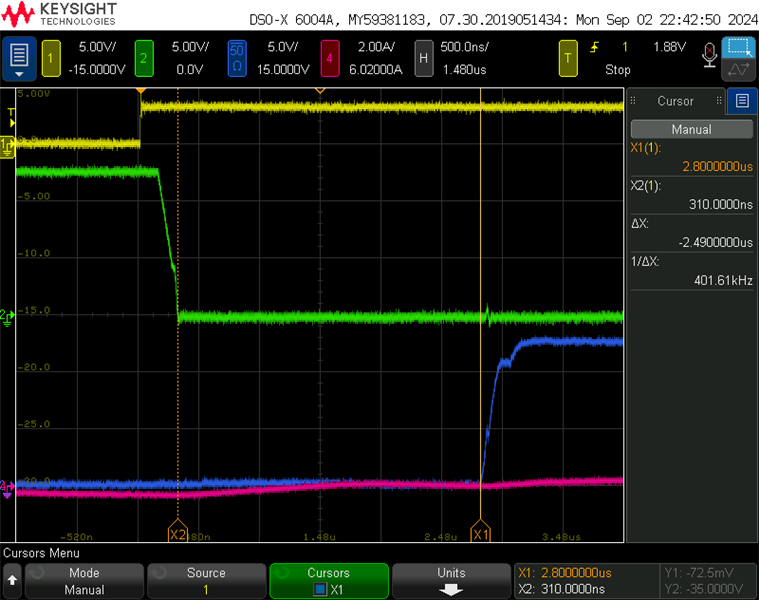

So GLx should start to increase the latest about 300ns after GHx reaches 0V. However I measure almost 800ns what is odd. The time increases / decreases when changing DEADT setting by about the right amount, but I have an offset of ca. 600ns.

The MOSFET used is BSC039N06NS.

CH1 (Yellow): GLx

CH2 (Green): SWx

CH3 (Blue): Phase current

CH4 (Red): GHx

Math (Pink): GHx - SWx = high side FET Vgs

I use quite generous settings for TDRVP (750ns) and TDRVN (464ns). Does this interfere with the dead time? As I read the diagram it should not.

Please advise.

Thank you and kind regards

Stefan