Tool/software:

Hi team,

I'd like to confirm with you on below understanding

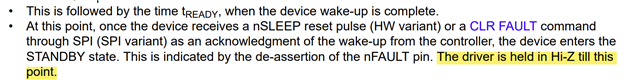

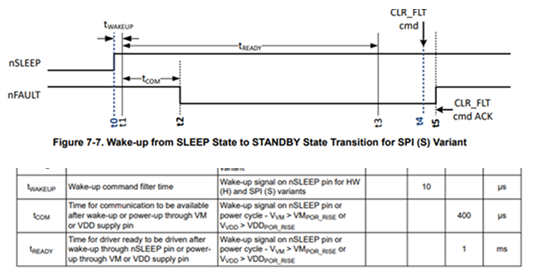

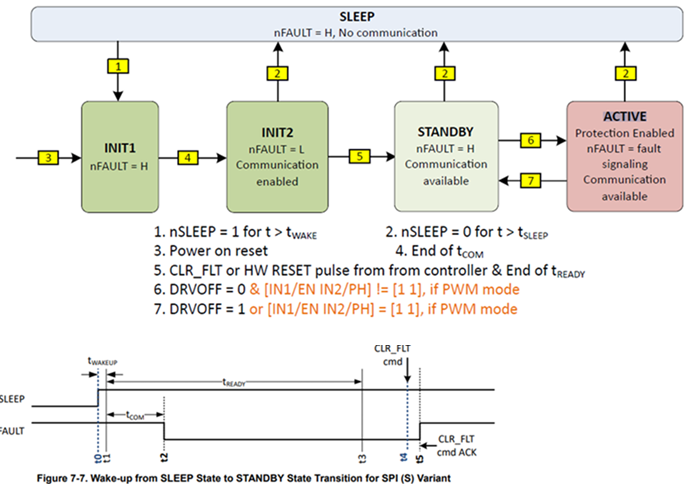

Our device EC table says after t2 communication is available and after t3 the driver is ready.

while at state machine my understanding is STANDBY (after transition#5) corresponds to t4. at the same time it says INIT2 communication enabled and STANDBY communication available.

Could you please help share:

What is the difference between "communication enabled" in INIT stage, and "communication available" in STANDBY stage?

If going back to the wake up sequence diagram, could we understand after t2 SPI communication is available, customer could set DRVOFF=0 and configurate duty cycle. Between t2 and t3, device could read DRVOFF/EN/PH related register status, but the driver has no output. The driver output will only be available after t3?

Thanks

Scarlett