Tool/software:

Dear Texas Instruments Support Team,

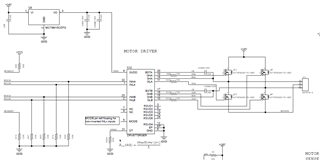

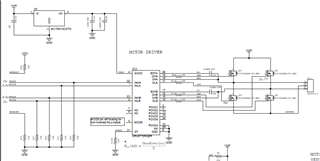

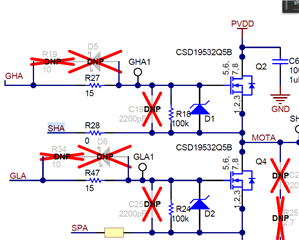

I hope this message finds you well. I am currently working with the DRV8770RGER motor driver and have a few questions regarding its operation. Specifically, my design which is attached to this message.

Could you kindly provide the following information:

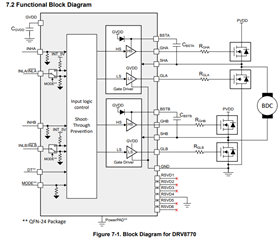

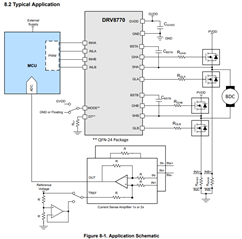

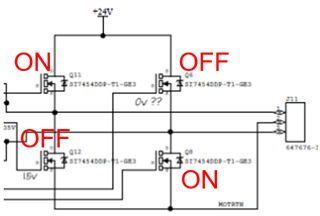

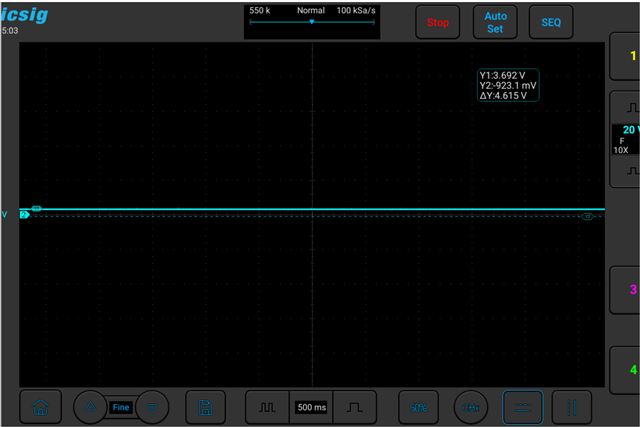

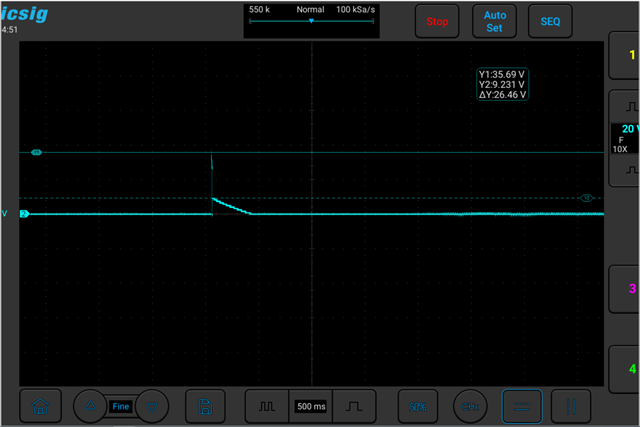

- What are the ideal input voltage and current levels that should be applied to INHA, INLA, INHB, and INLB to correctly trigger the outputs on the DRV8770RGER?

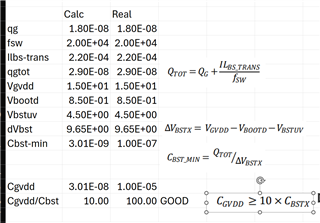

- Are there any specific conditions or limitations that should be considered for these input pins to ensure proper functionality relating to my design?

Additionally, I would appreciate your input on whether my current design, based on these parameters, aligns with the recommended operating conditions for the device. I want to ensure that the setup is optimal for the efficient and reliable performance of the motor driver.

Thank you for your time and assistance. I look forward to your response.