Other Parts Discussed in Thread: DRV8353, CSD19536KTT, UCC27301A

Tool/software:

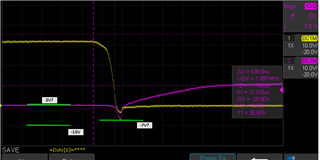

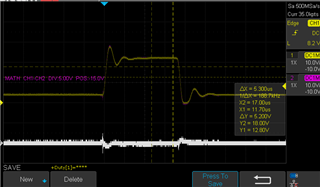

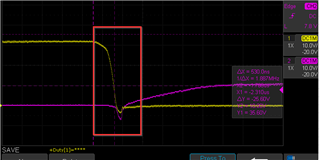

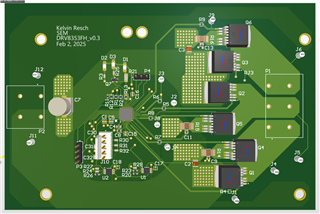

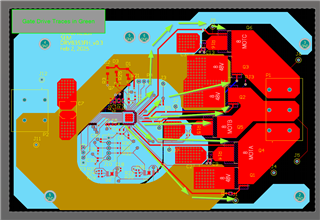

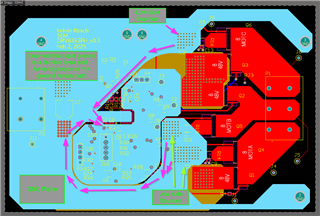

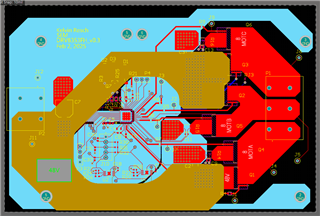

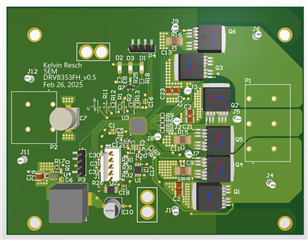

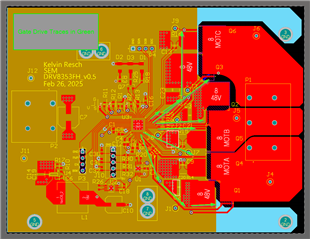

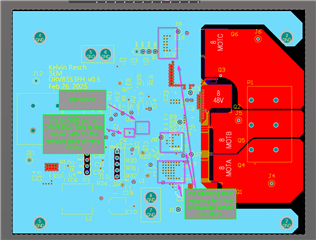

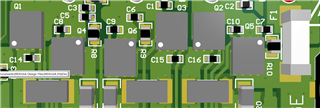

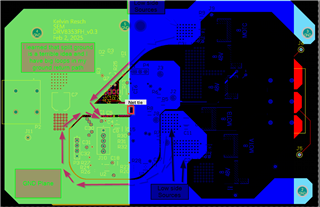

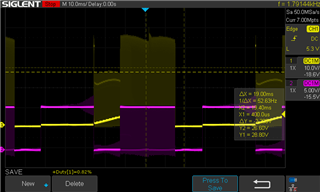

Hey everyone, I hope you're doing well. I have a question about BLDC commutation on the DRV8353F. I'm bringing up a motor controller that I built. It currently runs at 36V, and this scope trace was taken while running 0.5 A, but I will get it up to 48V 40A eventually. In the scope picture, pink is the lowside gate, and yellow is the highside gate for one of the phases.

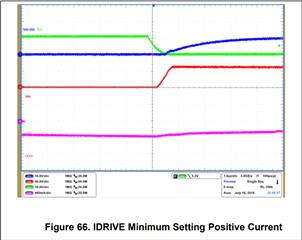

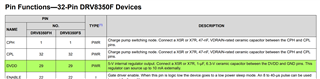

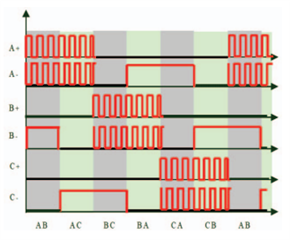

Before the PWM commutation step, the highside gate PWM at a lower voltage, and the lowside gate remains low. From what I understand, the highside gate shouldn't be PWM-ing in this phase. Here's a chart of what I think BLDC commutation should look like:

Let's say in my oscilloscope I'm measuring the B phase. I don't understand why, in commutation step AC (the second one), it looks like B+ is PWM-ing on my oscilloscope capture. I checked the other two phases, and they also look the same. Is this what the gate lines are supposed to look like? According to the commutation table (Table 8-3) on page 23 of the DRV8353 datasheet, it doesn't look like my highside gate should be doing anything in this phase. Also, I doubt it's a hall sensor issue because if I were in a commutation state for that phase, the lowside gate would be switching as well, but only the highside gate is being switched here.

I'd be really grateful for any advice or support here.

Thank you for taking the time to read this.

Cheers,

Kelvin