Tool/software:

Hi team,

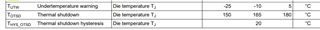

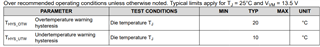

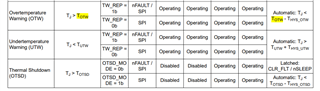

My customer is using OCP auto-retry function of DRV8889-Q1. They want to know whether there is risk when DRV8889 keeps retrying every 4ms under overcurrent condition for 1 minute. They are worried it may cause heat accumulating and damage device, especially under high Tamb, like higher than 100C. From my understanding, the device has thermal shutdown function, so there's no risk here. Could you share some comments?

Best Regards

Grey