Tool/software:

Hi team,

Regarding the use of the DRV3901QDGQRQ1 chip, I now have the following questions that need help to confirm;

1. In the specification book, the maximum low level of the pins SCLK, SDI, and SCS is 0.7V, and the minimum high level is 1.5V; generally, the high and low level limits of other TI chips are 0.7*Vcc and 0.3*Vcc. The high and low level thresholds of this chip are set lower. What are the considerations?

2. The high and low level thresholds are set too low, which may be easily interfered with. What aspects should be paid attention to when laying out the SPI communication pins?

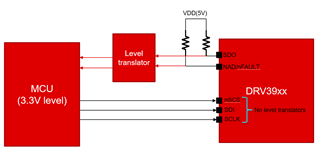

3. The microcontroller I currently use is powered by 3.3V, and the pin VDD power supply of the DRV3901 chip is 5V; the pins SCLK, SDI, and SCS in the SPI communication are directly connected to the microcontroller without level conversion, while the SDO pin is connected to the microcontroller after level conversion; Is it possible to handle the SPI pins of the DRV3901 chip in this way?

BR,

Ethan