Other Parts Discussed in Thread: DRV8462, DRV8412, , DRV8262

Tool/software:

Dear TI support,

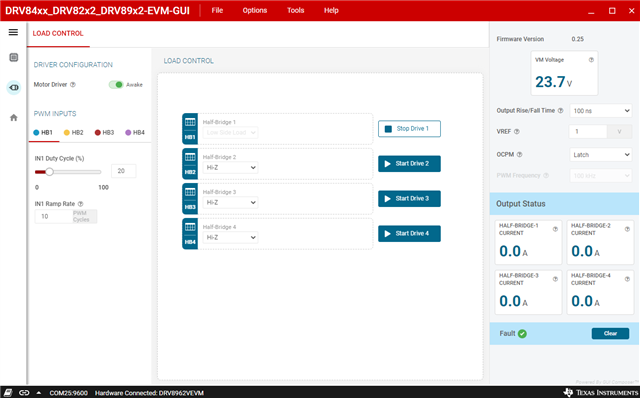

I'm facing issue in implementing a design that uses part DRV8962DDV.

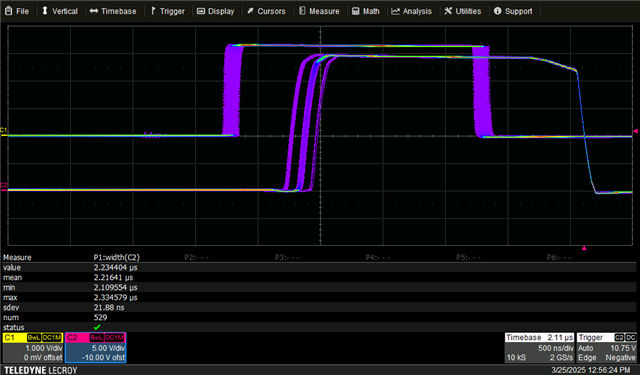

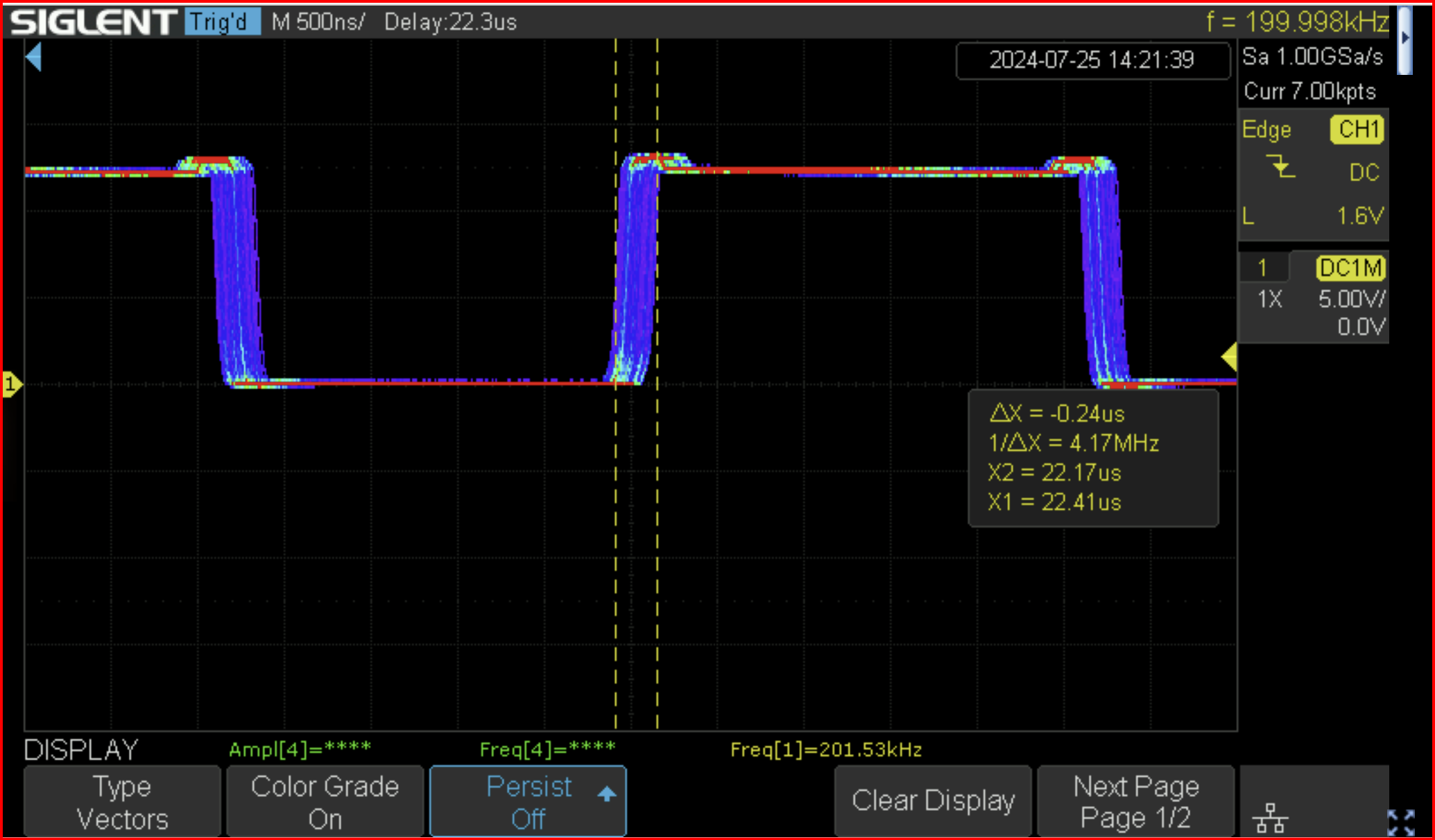

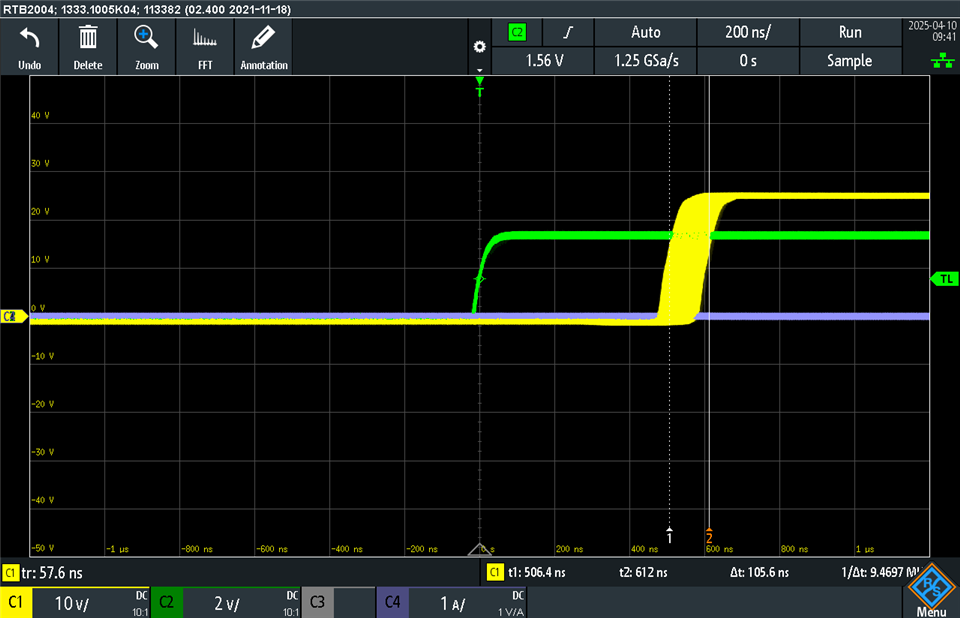

What I can see on the output of any of the four channel is jitter in the turn on and turn off time referred to the INPUT IN signal.

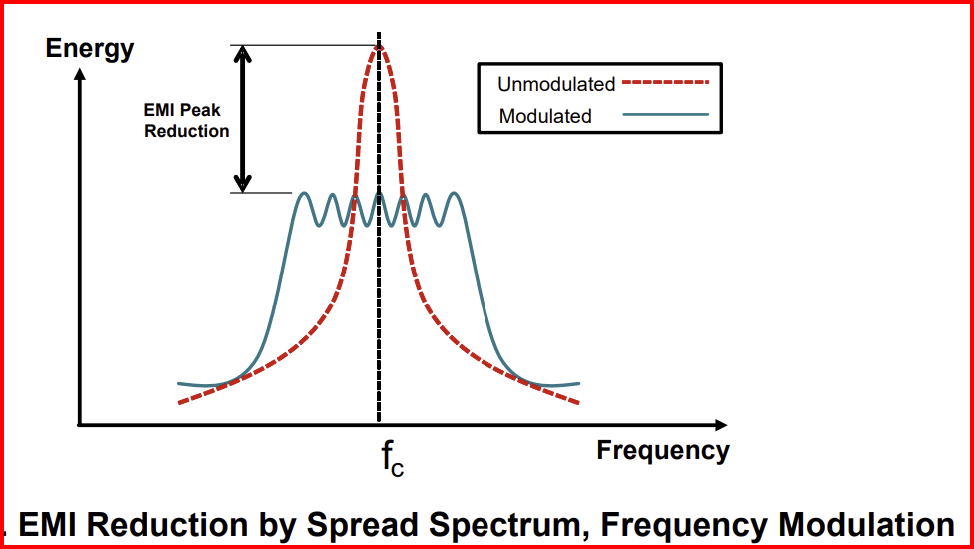

Specifically, what seems odd is that there is a deterministic distribution of the jitter, which in turn makes the application underperforming ( excess noise in the output voltage after LC filtering ).

EG: there is a discrete jump in the jitter of about 150nS, which changes the ON time compared to input signal. See picture for reference, measured on EVAL.

This behavior is present in both our design and in the evaluation board, at all duty cycle, with or without load. Tested at PWM frequency of 100kHz and 200kHz.

Please advise if this can be fixed or if it has to be considered in specs for the part.

Best regards,

Antonio

channel 1 INPUT

channel 2 OUTPUT