Tool/software:

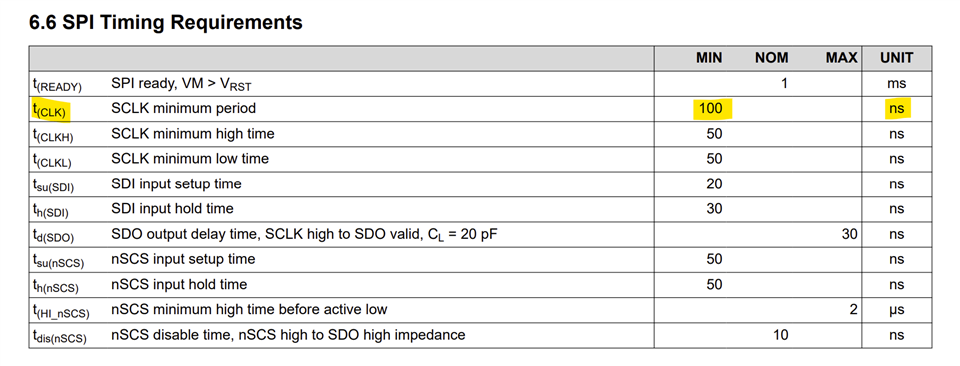

SPI is currently set to mode 1, that is, CPOL is 0, CPHA is 1, what is the communication frequency range of SPI?

The measurement of the FAULT foot has always been low level, may I ask whether the foot has always been low level can be eliminated through software control?

After the gui_loop is initialized, it enters the GUI_loop. If it is not possible to wake up the chip by gui_loop, what should I do