Tool/software:

[Question]

For Open Load detection.

Is it possible that nFAULT pin does not indicate the error(Low) while there is Step signal if Motor is set to Open?

Fault is only detected if there is no Step signal?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

[Question]

For Open Load detection.

Is it possible that nFAULT pin does not indicate the error(Low) while there is Step signal if Motor is set to Open?

Fault is only detected if there is no Step signal?

Hi Masanori,

Thank you for posting in this forum.

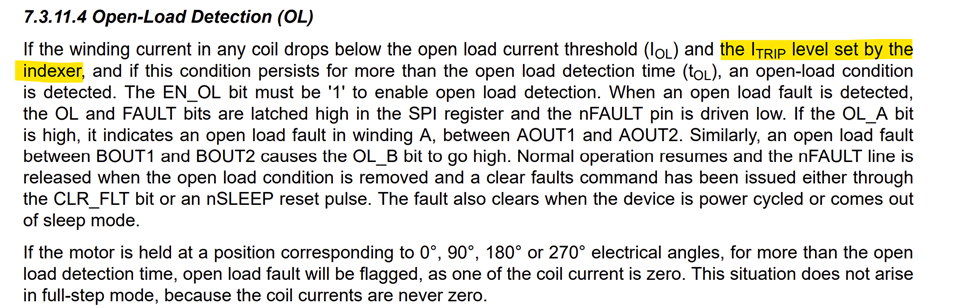

The open load detection latches the nFAULT and OL bits if:

1- EN_OL bit must be 1

2- Winding current in any coil drops below the open load current threshold (IOL) and the ITRIP level set by the indexer

3- This condition persists for more than the open load detection time (tOL)

Also when OL is detected the DRV8889-Q1 is working but report the OL by latches the nFAULT.

As noted, OL is detected when the criteria 1 to 3 satisfied. even if the step signal is applied to the DRV.

Please let me know if you have any more questions.

Best regards,

Mojtaba.

DRV8889 Open Load detection.xlsx

Thank you for your reply.

I attached about our result.

If it is possible, can you check it?

Hi Masanori.

Thanks for your update.

I checked you schematic and need to consider following points:

1- Use a 100 uF bulk cap on the VM pin.

2- Why did you use the series resistor on the SDI, SCLK and SDO pins. Also the pins are internally pull down and you do not need to pull it down externally.

3-nFaULT IS AN OUTPUT pin and is not be pulled up.

For your reference, please use the design file for DRV8889EVM can be downloaded DRV8889-Q1EVM Evaluation board | TI.com under design file

After revising the design, please check the nFAULT and nSLEEP signals under OL.

Please let me know if you have any issue after revising the design.

Best regards,

Mojtaba

I checked you schematic and need to consider following points:

1- Use a 100 uF bulk cap on the VM pin.

2- Why did you use the series resistor on the SDI, SCLK and SDO pins. Also the pins are internally pull down and you do not need to pull it down externally.

3-nFaULT IS AN OUTPUT pin and is not be pulled up.

For your reference, please use the design file for DRV8889EVM can be downloaded DRV8889-Q1EVM Evaluation board | TI.com under design file

After revising the design, please check the nFAULT and nSLEEP signals under OL.

Please let me know if you have any issue after revising the design.

Thank you for your reply. I appreciate it.

But if the motor is shorted, the Fault pin is continuously low.

Therefore, I do not think that the Fault pull-up is the main factor.

Are there any other possible factors?

Hi Masanori,

Yes that is correct. The nFault should be pull up.

Would you please check the nSleep while the OL happens?

It sounds like the nFault is cleared. it can be issued either through the CLR_FLT bit or an nSLEEP reset pulse.

Best

Thank you for your advice, I will check it.

If the open condition is continuously kept open, is it a possibility that the fault signal might go high and low repeatedly?

The nFault latches when OL happens, but it can be cleared through: 1- CLR_FLT bit 2- nSLEEP reset Pulse 3- device is power cycled

But if the OL still exist, the nFAULT and OL bit goes high again.

Best regards,

Mojtaba.

Thank you for your reply.

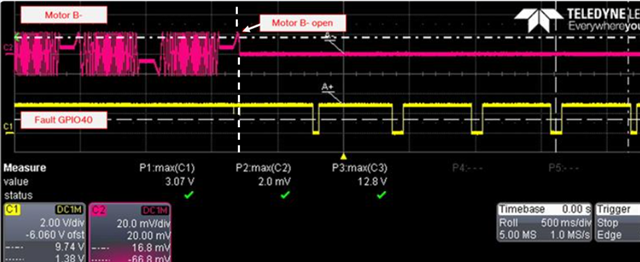

Pink is Motor B current. Yellow is fault signal.

If the Motor B is Open, the Motor current goes to zero.

Still, I want to know why the fault signal is not Low and repeats High and Low.

Hello team,

I add the information.

When both A and B are open, Fault goes to Low.

when only B is open, Fault seems to repeat H and L.

My customer would like to know the root cause or this issue.

HI,

Based on this capture, it is not clear how the nFAULT is cleared. Would you please show the nSleep with the motor current and nFault as well. If you can please provide the FAULT Status register.

Best regards.

Motjaba

Hi

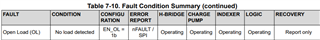

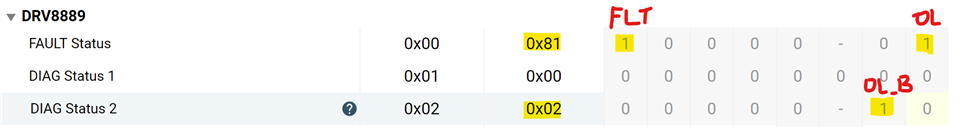

Under OL fault the DRV8889 is working under its normal operation as it is shown below:

Would you please clarify the reason that the STEP pulse is stopped when the nFAULT goes low?

Under OL fault the output voltage still exist. Would you please check the nSLEEP, current and nFAULT while OL happened.

Best regards,

Mojtaba.

Hello,

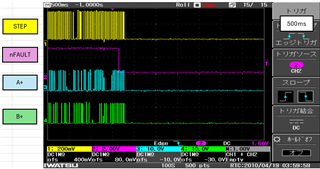

When the motor opens both A and B, the fault signal goes to Low. ⇒ Expected behavior

When only A is open, the fault signal goes to Low. ⇒ Expected behavior

When only B is open, the fault signal repeatedly High and Low. ⇒ Not expected behavior

The waveform result is attached. Could you please check it.

DRV8889 Motor OL detection.xlsx

Hello Masanori,

Thank you for all the information. There is a known issue with OL detection under the following conditions for this device. OL may not be detected when FSI < 0.96A and 1/64 or higher uSteps. As I checked your schematic, Vref is around 0.5V (to be confirmed). Also based on the register bit values shared in the previous excel DRV8889 Open Load detection.xlsx , the TRQ_DAC [3:0] is set at 87.5 % (to be confirmed). This means that full scale current FSI is 0.5A x 0.875 = 0.44 A. This may cause some issues. Please Let me investigate more about it and get back to you when I have update. I will keep this thread open to provide you more information.

Best regards,

Mojtaba.

Hello,

Thank you for your feedback and new information

Our register setting

TRQ_DAC [3:0] : 87.5 %

micro-step : 1/64![]()

Our customers require root cause and solution asap and I await additional feedback.

Hi Masanori,

Thank you for your patience. I am working on this issue and get back to you soon.

Best regards,

Mojtaba.

Hello Endo-san,

Thanks for sharing the register contents. Based on these settings the microstep setting is 1/8. However this is not related to the OL issue. Per the schematic, VREF = 0.5034 V or 0.229 A for 100 % TRQ_DAC. Since you have TRQ_DAC = 87.5 % the actual IFS current setting would be 200 mA.

Would it be possible to share the stepper motor datasheet? Specifically coil L and R values? Meanwhile, with the same register settings you had with 1/8 Step mode could you please repeat the OL test for B coil with IFS current set to 400 mA? If you perform this 400 mA for short period of time the motor will not overheat. But a quick check will be helpful to debug the issue. If nFAULT latches as expected you can try a lower current by -50 mA increments. Please also let us know the STEP input PPS used for OL testing. Thank you.

Regards, Murugavel

Hello

>Specifically coil L and R values?

coil L : 11mΩ (1kHz / 1Vrms)

coil R : 20 × (1±10%) Ω

>Please also let us know the STEP input PPS used for OL testing.

18432 pps

Hello Endo-san,

Thank you. L you meant 11 mH. The PPS seems high at 1/8 Step, I assume 18432 PPS was for 1/64 Step. With 1/8 Step 2304 PPS would give the same stepper speed as 18432 PPS at 1/64 Step.

While we do not have a stepper with the same specifications you mentioned we tested with an automotive headlight ADB stepper that had 10 Ω DCR and 12 mH L. The hardware used was a DRV8889-Q1, VM = 12 V, the IFS was set to 200 mA to match with your test setting. The SR was set at both MIN and MAX setting for the tests. The results did not change with SR settings.

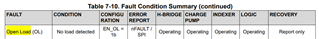

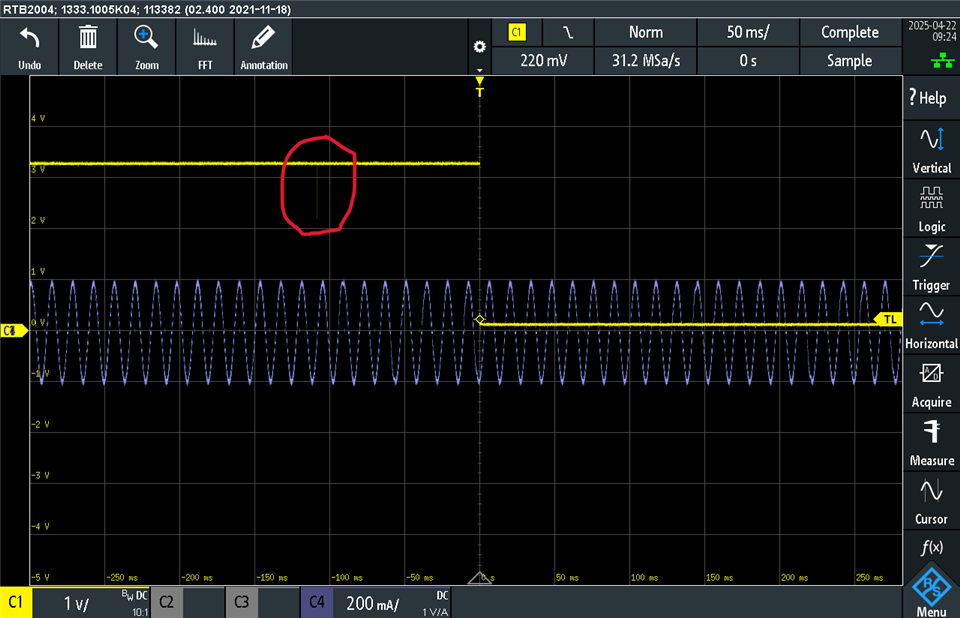

1/8 Step, 2304 PPS coil A open:

Note: I circled a spike on nFAULT which also happens on the GND and power rail because of the sudden disconnect of the motor coil while it was driven. From that spike about 160 ms later nFAULT goes low indicating an OL fault. The tOL specification for the DRV8889-Q1 is MAX 200 ms.

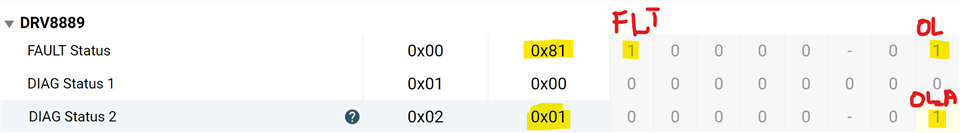

See below diagnosis registers readout:

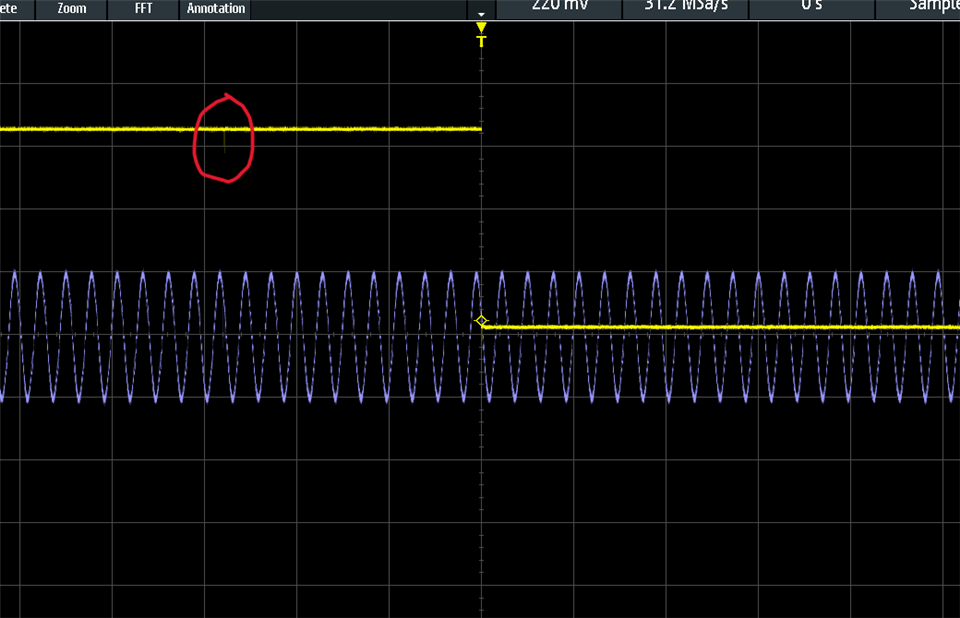

1/8 Step, 2304 PPS coil B open:

Note: Similar behavior as coil A open.

See below diagnosis registers readout:

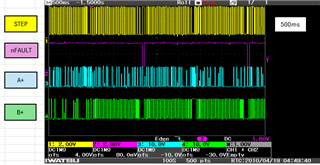

I repeated same tests with 1/64 Steps, 18432 PPS, IFS 200 mA. While the stepper was running at the same speed, OL was not detected with both coil A or coil B open load tests. The DRV8889-Q1 cannot open load for the following settings. Tested with 1/32 Steps, 9216 PPS, same limitation with OL detection. With 1/16 Steps, 4608 PPS, OL detection was functional for both A and B with SR setting 10.8 V/μs only.

The reason for this behavior is, for low ITRIP level values for the lowest microstep in high microsteps setting current regulation noise on the xOUTx node, LS-FET drain causes glitches that resets the internal OL timer continuously and unable to report an OL condition. These glitches are dependent on the IFS setting, motor R and L including cable harness and VM supply voltage. Increasing IFS current also could alleviate this situation as higher ITRIP level for the high microsteps' lowest steps would have less noise glitches.

Note: OL can be detected with 1/32 Steps, 9216 PPS, SR 10.8 V/μs only when the decay mode was changed to STDD, dynamic decay. In this decay mode Stall cannot be detected. The glitches are less in STDD at these low current microsteps.

Please try with 1/8 Steps and 2304 PPS. I also want to add the stall detection function if needed would perform more reliably with 1/ 8 Steps vs. 1/64 Steps. The reason is the number current regulation tON and tOFF cycles within a microstep period would be lower with higher microsteps. tOFF is used for computing torque count for stall detection. See this application note for details, https://www.ti.com/lit/an/slvaei3/slvaei3.pdf.

Thank you.

Regards, Murugavel