Tool/software:

Team,

What's the purpose of this VDRAIN slew rate on design? Could you help to explain it more! very thanks.

Regards

Brian

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Team,

What's the purpose of this VDRAIN slew rate on design? Could you help to explain it more! very thanks.

Regards

Brian

Hey Brian,

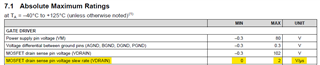

The Vdrain voltage states the voltage rise/fall spec on the Vdrain pin when supply voltage is applied on the device. This slew rate specifies the abs max rate before we damage the driver circuitry. The vdrain voltage is not a switching voltage and the rise/fall is gradual due to the presence of bulk caps on vdrain.

Best,

Akshay

Thanks. Customer is surprise that the device is damage when rise/fall >2VuS and VDRAIN pin is under abs,max of 102V.

Customer originally thought is that the slew rate limit is for the voltage sensing response.

If this is a case, where of the internal circuitry could be damaged when slew rate is violated? Could you point out it and explain how come it's damaged? Thanks.

Regards

Brian

Hey Brian,

I am curious on why the customer thinks they will violate this spec in their application at all. The cap on Vdrain should be more than enough to slow the voltage change on the pin to be within range.

Do we have any background on this question?

Best,

Akshay

Thanks. I have no ideal about the situation in application now. However, what’s the slew rate in general if there is a bus cap on VDRAIN pin ?

regards

Brian

Hey Brian,

I cant say specific time without knowing how much capacitance there is on board and how the board is being supplied. But I will say that I have not seen this to be a point of concern from customers yet. That is why I am curious on why the customer is even inquiring about this spec.

Best,

Akshay

Thanks. Since you mentioned it could be damaged once violation, customer is just worried if something would be happened in the application. as you know we're discussing with Ryan and Joseph on failure damage during short test event.

after checking with RDs, in the power on test, yes there is no problem with slew rate. it's only about 0.002V/uS (0V to 5V with 200mS timeframe)

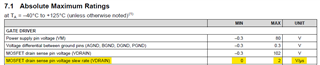

however, when in the short-test, customer found the VDRAIN is already over the 2V/uS as shown below. it is about 9V/2uS and violating the spec. Could you check if there's a problem. if not, why? thanks.

Regards

Brian

Hey Brian,

Let me check in with the team if we have some more info on this.

In your waveform are you measuring VDS across the FET correct? Do you see have a waveform of Vdrain to GND measured at the driver pin during these conditions?

The damage during your short test might have other structures that could have been damaged. Do you have impedance measurements between good and damaged parts?

Best,

Akshay

Hello Akshay, The waveform (C3) was measured between the VDRAIN pin to GND pin of DRV during test. It already violates the 2V/uS, correctly? With this higher slew rate, can device be damaged possibly? Customer would like to know if it's a risk with slew rate?

Regards

Brian

Hello Brian,

Understood, Let me wait for feedback from the team.

I also noticed that there is an undershoot on VDS, which would indicate there maybe an abs min violation on SHx pin wrt to gnd. This can damage the predriver structure.

Best,

Akshay

Hey Brian,

The vdrain slew is technically in violation of the spec. The Vdrain pin is connected to the charge-pump circuitry, the pre-drivers stage and few other important blocks and the vdrain node is not expected to violate the 2V/us spec from design to ensure that the rest of the connected circuitry work as expected. When we violate the spec it is hard to tell what all fails and in which order as there are some internal protection circuitry and clamp diodes that would be at risk.

I am also surprised that there is that much slew on vdrain node with all the capacitance on Vdrain.

I think it makes more sense to focus on the SHx voltage. The VDS seems to have an overshoot, indicating a SHx abs min violation. This is beyond the DS spec and could have also gotten damaged.

What is the customers goal from this short test?

Best,

Akshay