Tool/software:

Hello,

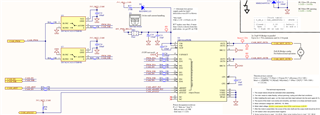

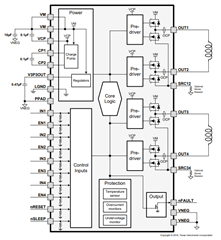

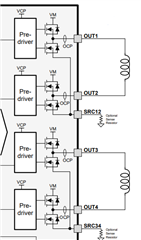

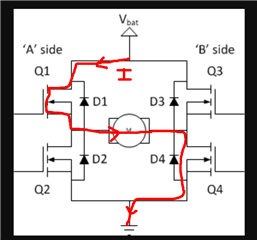

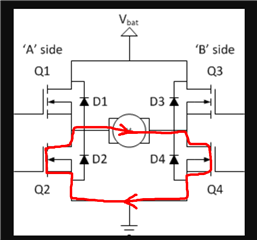

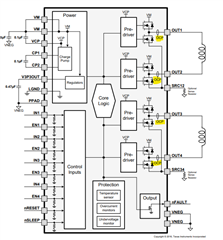

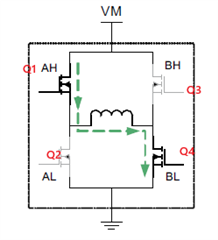

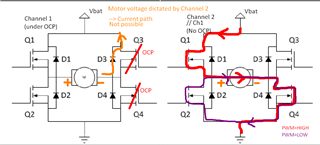

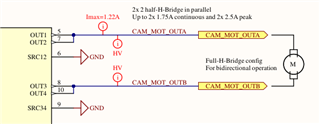

We are currently using the DRV8844 in order to drive a DC motor with slow decay. We are connecting the two outputs of the driver in parallel in order to increase the maximum current that can be drawn from the driver.

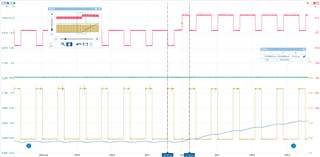

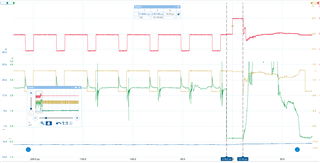

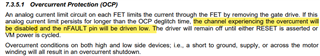

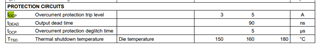

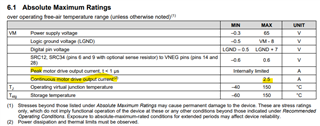

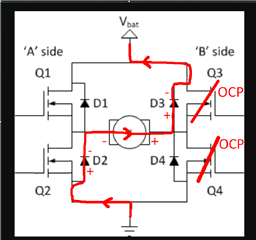

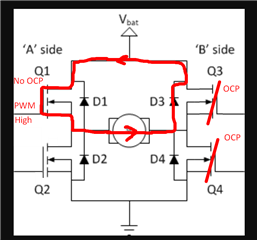

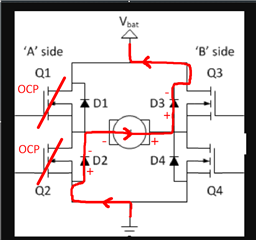

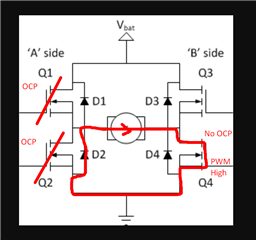

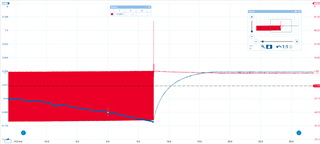

For our test, we are driving the motor with a PWM 48V @ 32kHz with a duty cycle 30%. The motor is stalled shortly after startup. As shown in the picture below, the output PWM (red) is applied, and the current (blue) is increasing up to a maximum value of ~8.64A. This value seems already quite high, since the over-current protection is supposed to trigger at 5A. At the failure, a spark is visible on the chip, and it is unusable afterward.

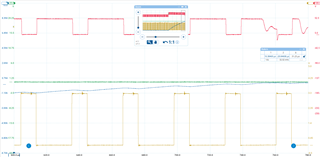

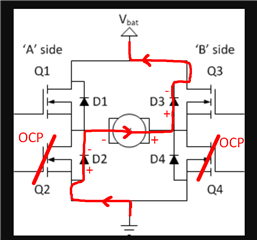

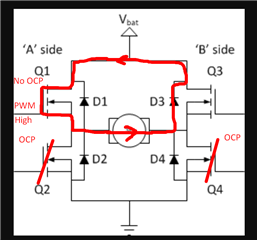

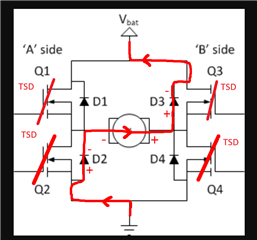

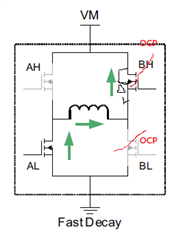

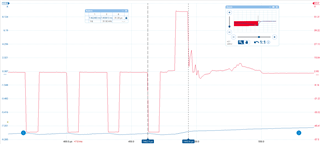

Let's zoom in at the time of the failure. We can observe that the PWM is performing its job properly. When the current is at its highest value, we observe an inversion of the voltage applied to the motor. The failure occurs when the PWM should go low again, causing the driver to burn.

- We don't think that it is related to our control since the PWM that we are applying are at non-zero voltage at the begining of the cycle. In this image it is clearly at the end of the cycle that the voltage is inverted at the output of the driver.

- We think this might be related to the slow decay, but we would need some support to verify that. Any other clues to find out the cause of our issue is also welcome.

- Performing the same test with a PWM of 20%, the current reach a value of 6A, but does not cause the driver to fail. Eventually the driver will enter in error due to over-temperature (we have a thermal camera measurement that confirms this). So our issue seems to be related to the high current consumption.

I remain available if you need additional information describing our issue,

Thank you for your responses!