Tool/software:

Dear Team,

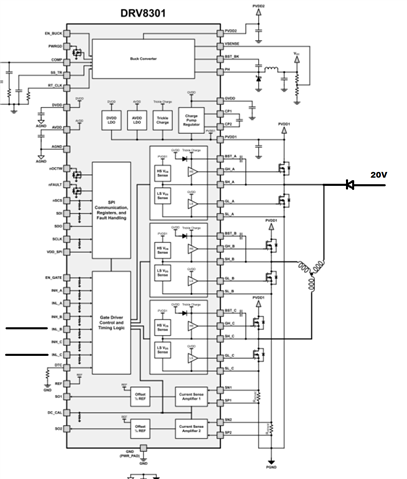

I am doing a special use of the DRV8301. In fact, the design is as a standard BLDC use but I need for a special situation to drive 2 low side (and only these 2 low side) with the third phase at a define voltage.

See the picture below. I would like to drive the low side phase B and phase C with a voltage applied on phaseA.

Not any high side will be driven.

In this configuration, the driver seems in fault mode and not driving the external mosfet but nFault output is not active.

If the BLDC is unconnected, low side are driven but not in case of BLDC connected.

Seems that a fault is detected if voltage is applied on any phase.