Other Parts Discussed in Thread: DRV8353

Tool/software:

Hi All

I have a question about DRV8353F.

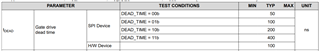

(1) As stated in the document Understanding Smart Gate Drive, will the dead time change because the dead time is optimized?

https://www.ti.com/jp/lit/an/slva714d/slva714d.pdf

Or is it fixed at the standard value described in the specs below?

(2) It is stated that the operation when SPI is overcurrent operates in cycle-by-cycle (CBC) mode by default, but does this mean the same as Automatic Retry in OCP_MODE?

(3) We are considering both the DRV8353F (40 pin) and the DRV8353 (40 pin), and plan to use a common layout.

The DRV8353 data sheet does not include a reference layout for the 40 pin. Is it okay to use the same layout as the DRV8353F data sheet?

Best Regards,

Ishiwata