Tool/software:

Hi,

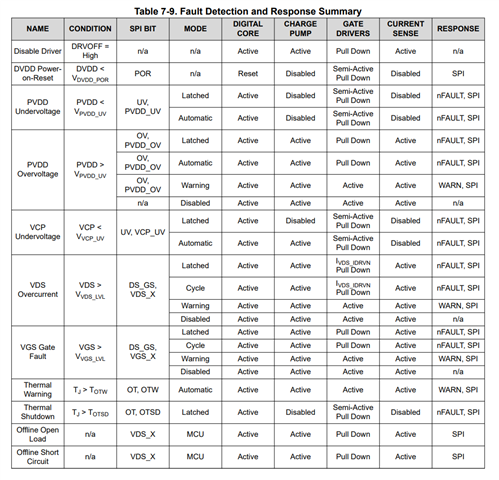

I have configured the UVOV_CTRL register with the value 0xF4. With this setting, I observed that the FAULT pin is asserted when the power supply voltage exceeds 28.5 V. However, the corresponding fault bit in the status register does not indicate this condition.

As per my understanding, setting 0xF4 should disable the PVDD supply overvoltage monitor mode. Given that, I’m unable to understand why the FAULT pin is still responding to voltages above 28.5 V.

Could you please help me understand this behavior?

Thank you for your support.

Best regards,

Kartha