Tool/software:

Dear

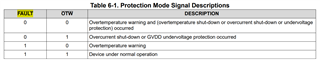

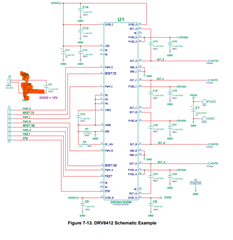

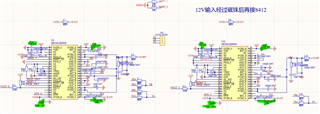

MP: When using the 8412 parallel drive output and increasing the drive current solution, the peak-to-peak output current of the chip is 7A. The IC is prone to protection. What is the reason for this?

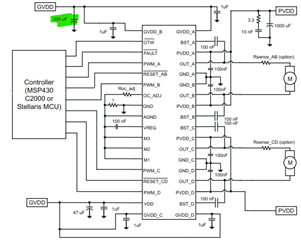

The current configuration resistance is 27K, Two chips are connected in parallel with three half-bridge outputs to drive a three-phase stepping motor.