Tool/software:

Hi expert,

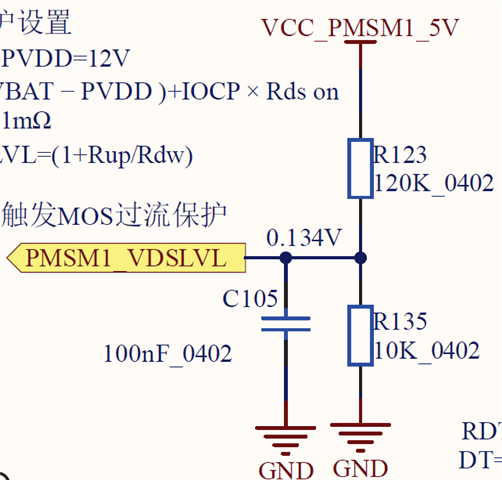

My client is currently using DRV8329, when the circuit is powered on without load, the MCU provides a drive signal, but the device is unable to operate, and the nfault pin remains pulled low. After investigation, disabling the Vds overcurrent protection feature( by connecting VDSLVL to GVDD through a 100 kΩ resistor. ) allows the device to return to normal operation.

After testing, the MOSFET turn-on time is about 500 ns, with the load current being 0. I would like to know

1. what causes the nfault pin to be pulled low constantly.

2. Currently, disabling the Vds overcurrent protection can allow the circuit to resume operation, but it loses overcurrent protection functionality. How can this be improved?

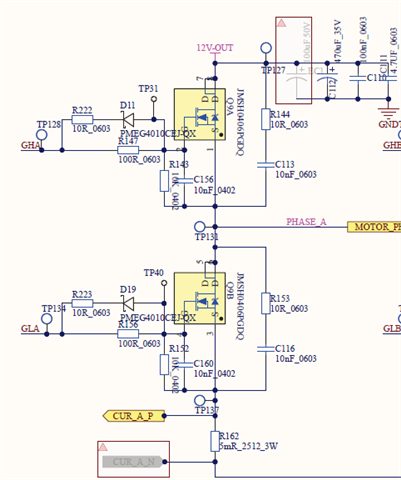

Below are some schematics:

VDSLVL

drive circuit