Other Parts Discussed in Thread: TMS320F2800156-Q1, DRV8334,

Tool/software:

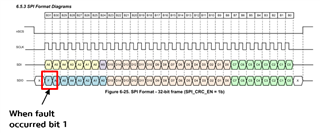

1) Fault occurrence in SPI communication

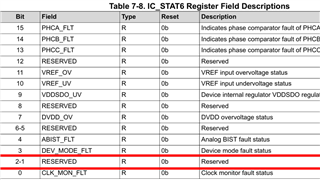

2) FAULT bit 1, SDO B31bit 1 of IC_STAT1 register (0x00h) when reading status register

3) No flag occurred when reading other status registers

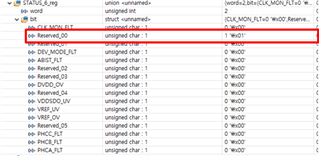

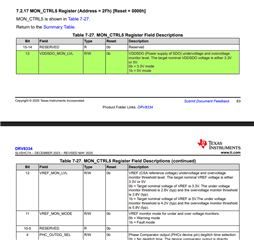

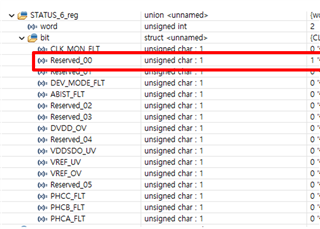

4) The bit corresponding to Reserved in IC_STAT6 is set to 1

Q. Why is the reserved bit set to 1? Please tell me how to solve this.

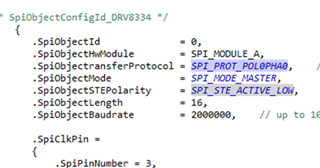

MCU : TMS320F2800156-Q1

MCU SPI option