Tool/software:

I am working with a 3v3-powered processor and want to protect its inputs. Are there any issues, specifically on the nFAULT pin, that would come from using a 3v3 pull-up rather than a 5V?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

I am working with a 3v3-powered processor and want to protect its inputs. Are there any issues, specifically on the nFAULT pin, that would come from using a 3v3 pull-up rather than a 5V?

Hello Aleksandra,

Thanks for the question.

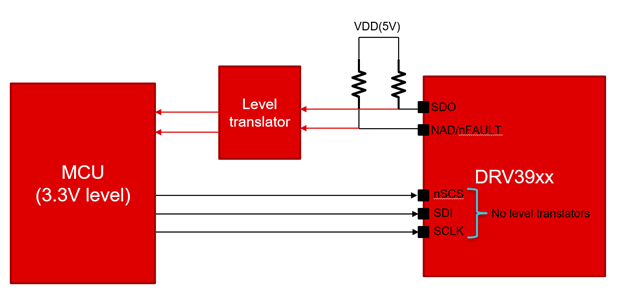

VDD operates at 4.5-5.5V in DRV3946-Q1. The pull up on NAD/nFAULT and SDO pin needs to be to VDD. You can use level shifters in the following configuration

Thanks,

Ibinu

Hello Ibinu,

I've made the board so that the nfault is pulled up to 3v3. We are still able to program it with an assumed high impedance (node 3 address) The driver is powered with 5v. What are the drawbacks from keeping the nfault pin pulled up to 3v3? The outputs are fine as the processor can accept up to 5V signals, moreso concerned what the nfault pin itself will do.

Hi Aleksandra,

The nFAULT/NAD pin is used to determine address during powerup by drawing a current from the pin and comparing the voltage with respect to VDD.

I think you are able to see it working since the Node address is 3, which is the highest. However this cannot be guaranteed across conditions like temperature and device.

Thanks,

Ibinu