Tool/software:

Hello team.

I would like to know what the path will be when 5V is applied to the NSLEEP/DRVOFF/NSCS terminals while PVDD and DVDD are open.

As ECU of the failure mode check, we check the behavior of the IC when the power supply is in an open state.

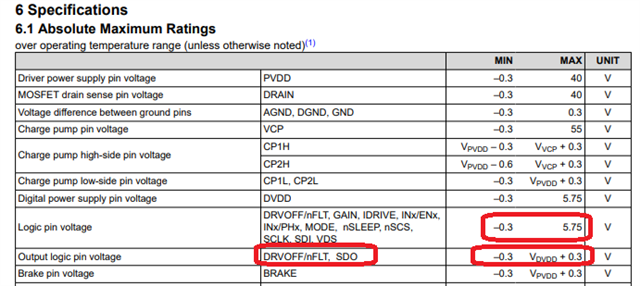

When we reproduced the situation where the MCU did not notice that the pre-driver power supply was open and supplied 5V to NSLEEP/DRVOFF/NSCS, we confirmed that voltage was leaking into the following terminals.

・SDO:1.6V

・DVDD:1.2V

Could you please answer the following two questions?

1. What path does voltage take to appear on the DVDD and SDO pins?

2. What causes a voltage difference between the DVDD and SDO pins?

Best regards,

Saito