Tool/software:

Dears,

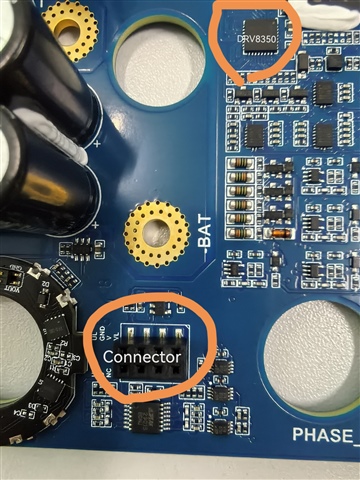

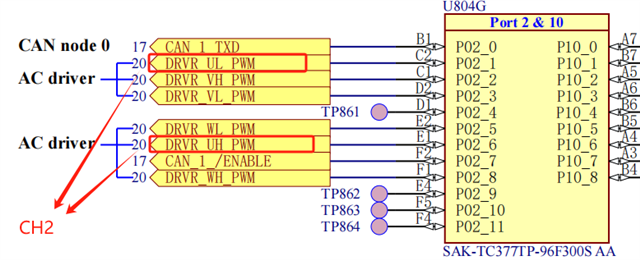

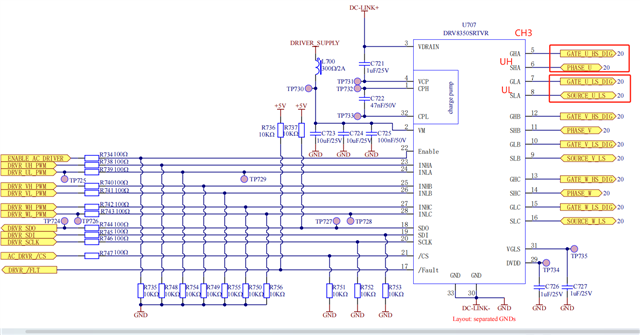

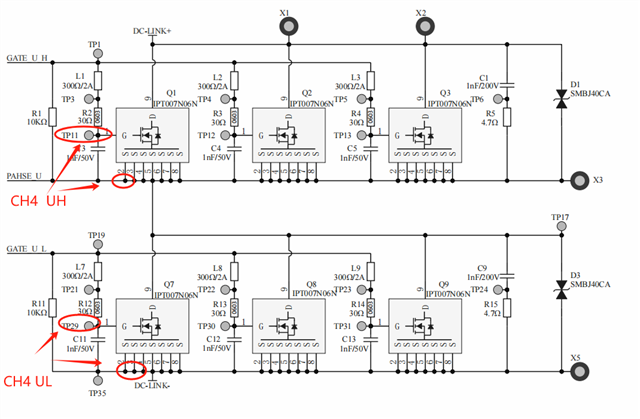

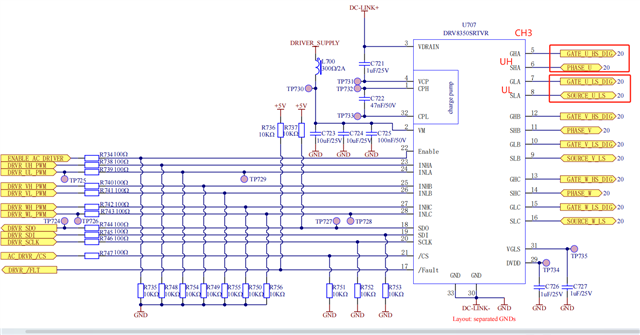

The customer uses DRV8350 in the application scenario of electric forklifts, with a 24V system and a three-phase asynchronous motor as the load. The motor power ranges from 1.5KW to 3.0KW. Use DRV8350SRTVR to drive MOSFETs (each half bridge arm is used in parallel with 3 Infineon IPT007N06N). The Qgd of a single Infineon IPT007N06N is 39nC, and the Qgd of three in parallel is 117nC. According to DRV8350 manual 9.2.1.2.2, the Idrivep range is calculated to be 390-1170mA, and the Idriven range is 780-2340mA. The Idrivep set on the software is 600mA, and the Idriven is 1300mA, which meets the requirements.

During the vehicle reinforcement test, the 3.0KW model was tested for more than 30 hours without any abnormalities; However, the 1.5KW model underwent three consecutive reinforcement tests and all showed DRV8350 damage. The malfunction occurred during several hours to over ten hours of vehicle testing, all of which occurred during the process of carrying the vehicle forward.

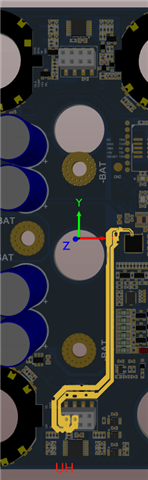

Check the software, read the register, and display GDF. The driving current of the bridge arm on phase U is too high; Check the hardware, three times there was a short circuit or low impedance between pins GHA and SHA of DRV8350, while all other components were normal. Check LAYOUT and no abnormalities have been found in the three half bridge drive signal lines. May I ask under what circumstances this GDF may occur? What are the directions for troubleshooting problems?

Thanks.