Other Parts Discussed in Thread: DRV8876, DRV8876EVM

Tool/software:

Hello Team,

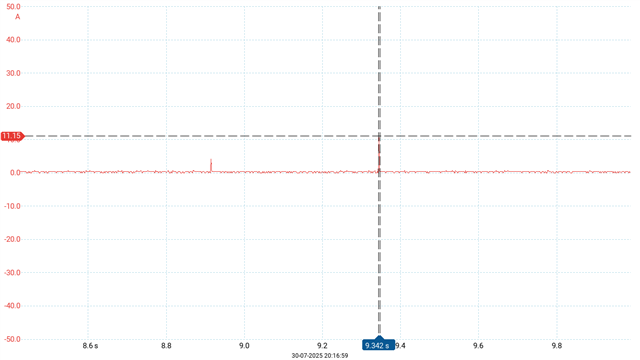

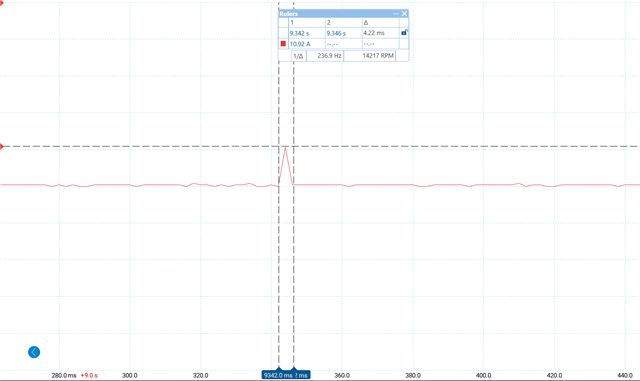

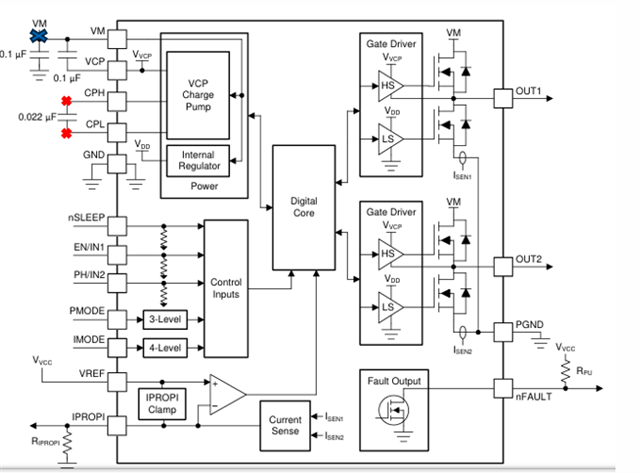

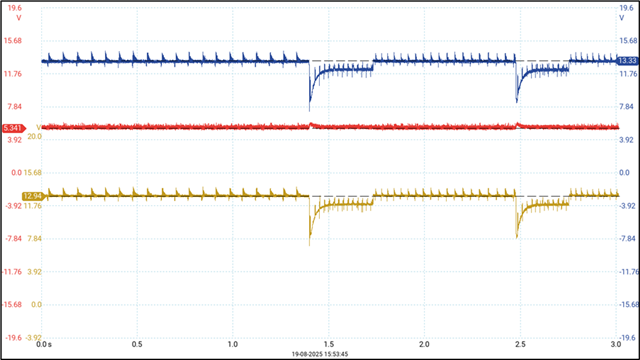

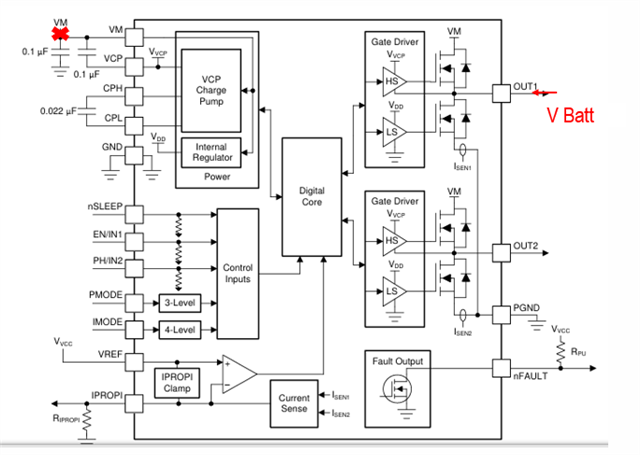

I have been testing the DRV8876 for my application, as a part of it we connected VDC(+12V) to VM and negative terminal to OUTA and the GND and PGND terminal were floating. Initially the a high current of 13A pulse is drawn by the circuit later no changes were observed. The IC tested and it found in good condition, I couldn't understand how it changed it's behavior of the circuit? Can the fault pin can trigger without any reference point(GND/PGND)?

Regards,

Jishnu K