Other Parts Discussed in Thread: DRV8329

Tool/software:

Hello

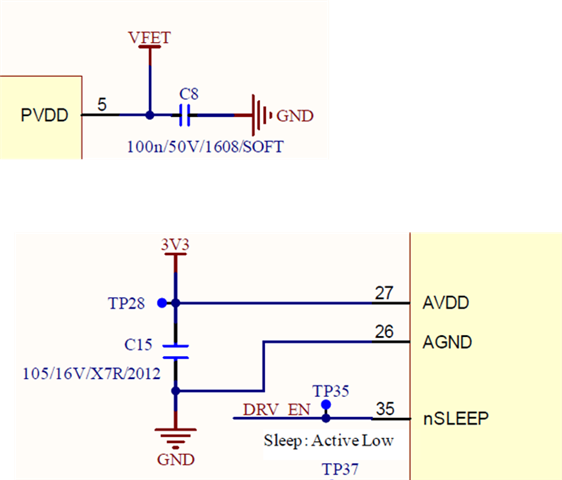

We have designed TI IC That MCU and Gate Driver (MCU : F2800156 / Gate Driver : DRV8329-Q1)

But, There is problem so please check and give solution

1. Situation

-

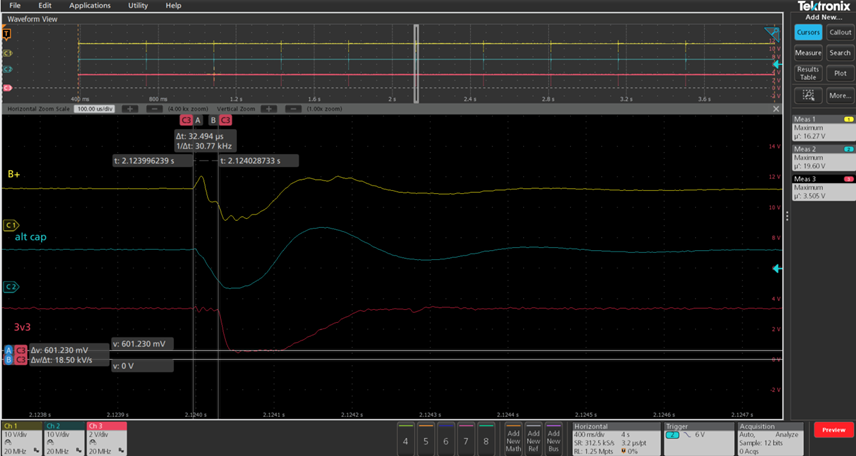

During the phase-to-GND short-circuit fault diagnostic test, the fault cannot be latched/confirmed.

-

Root cause: When the short occurs, the gate driver supply voltage drops momentarily, which causes the 3.3 V rail for the gate driver and MCU to sag.

-

As a result, the MCU (TI F2800156) resets and fault confirmation fails.

-

Gate Driver used: DRV8329-Q.

2. System Conditions

-

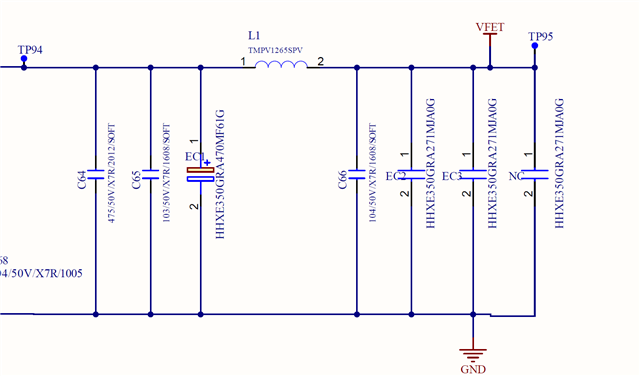

Please refer to the attached schematic.

3. Constraints

-

The MCU must sustain operation for the required hold-up time (refer to datasheet).

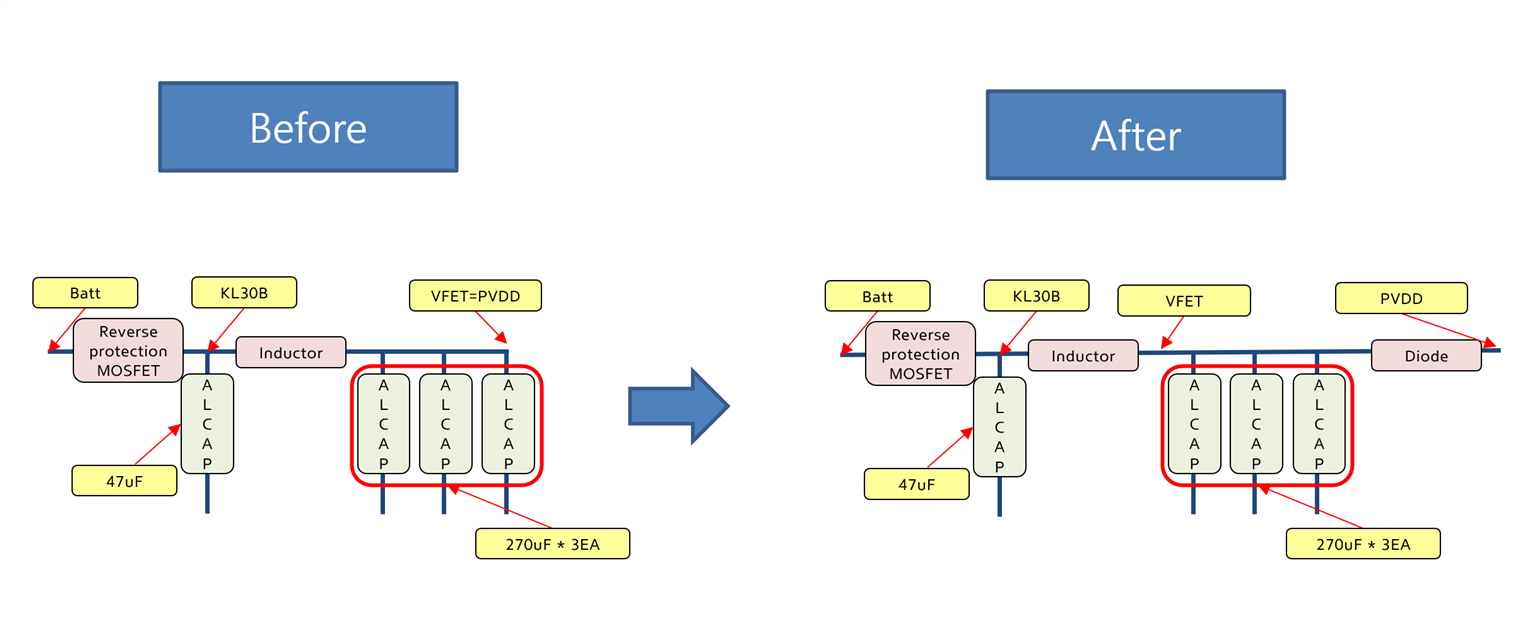

4. Attempted Solution

-

Added ~600 µF capacitor on the 3.3 V rail, but this is not a practical solution.

Request

Could TI suggest a practical solution to prevent the MCU from resetting under this condition?

Schematic and waveform data are attached for your review.

-

Input: 12 V

-

POW_SUP: Node after the battery → filter → reverse polarity protection FET