Other Parts Discussed in Thread: DRV8305

Tool/software:

Hello,

I have had this issue once before:

and the problem was easily solved, since the VCPH to PVDD cap at 2.2nF and not the recommended value of is recommended to be 2.2uF.

After changing the cap to the right value, everything was okay.

Now, I have a similiar issue on a new revision of the same board. The only things that have change

are a reduction in the size of the cap for CP1 and CP2 from 0603 to 0402, and an update to the

new land pattern as described in the Datasheet SLVSD12D. The current to the board is at 77 mA

when the EN_GATE is cleared and when set jumps to 318 mA where we would expect 150 mA as

in the earlier version of the board.

I have checked the sizing of the passives around the part, set the IDRIVE currents to minimum,

looked for any mistakes in the new footprint and I do not see the mistake.

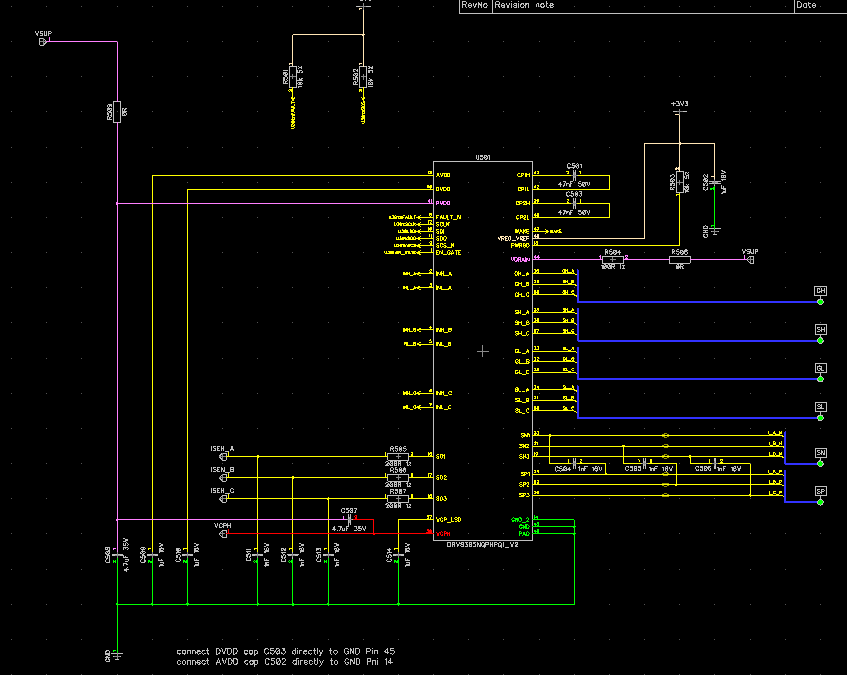

Here the Schematic:

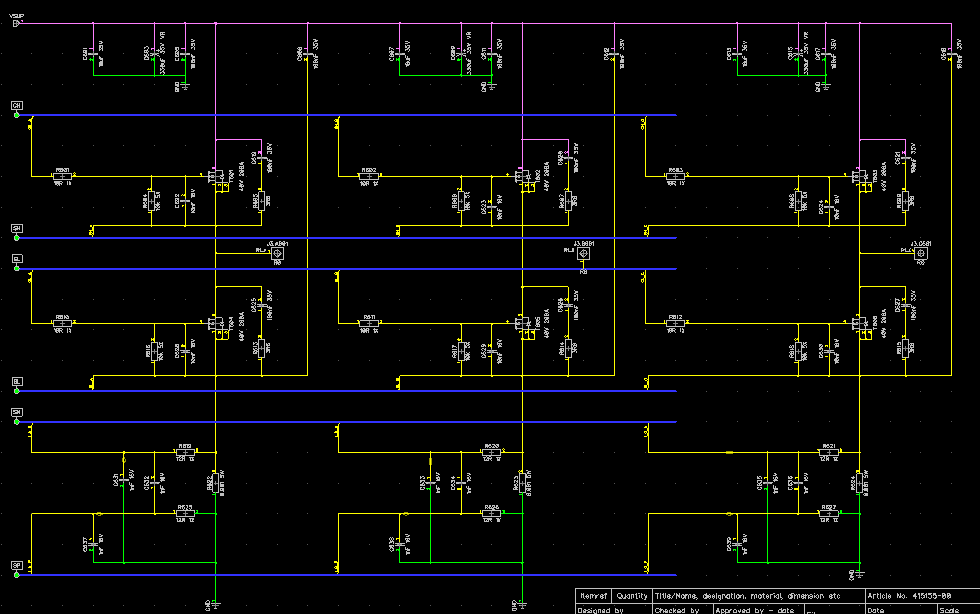

and the schematic of the power stage:

Neither the chip nor other parts are exceptionally hot, but maybe 2 °C warmer as compared to the earlier version of the board.

Any Ideas are much apprecitated.

Kind Regards,

John