Tool/software:

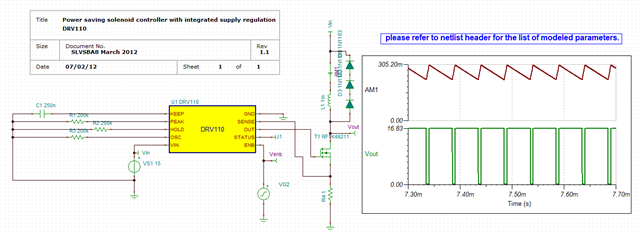

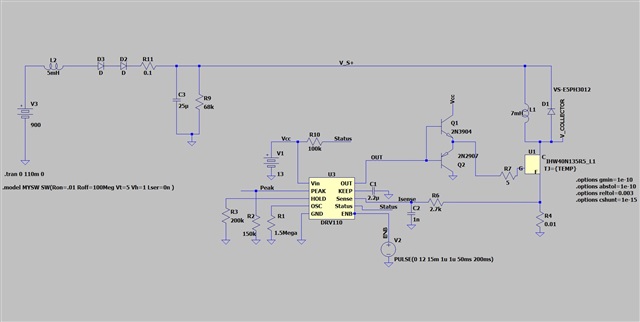

Hello, I'm trying to simulate the DRV110 in LTspice but seems that there is something wrong in the model, in pratical the regulation of the PWM is not like is aspected to be, here the test circuit:

.

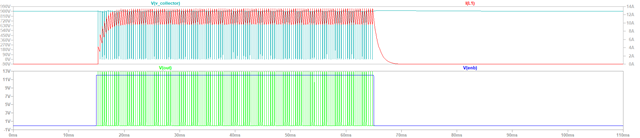

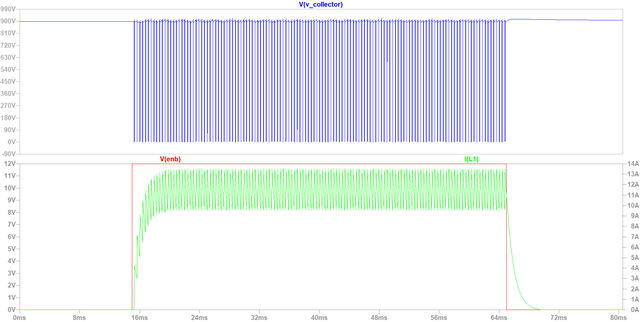

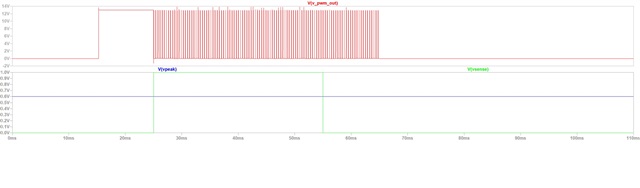

We can see that when the sense signal is lower than the Vpeak level the output goes high and when the sense signal is higher than the Vpeak the DRV110 reduce the duty cycle to 10% max, but when the sense signal go down to the Vpeak level the dudty cycle doesn't change and stay at 10%.

On model lib file:

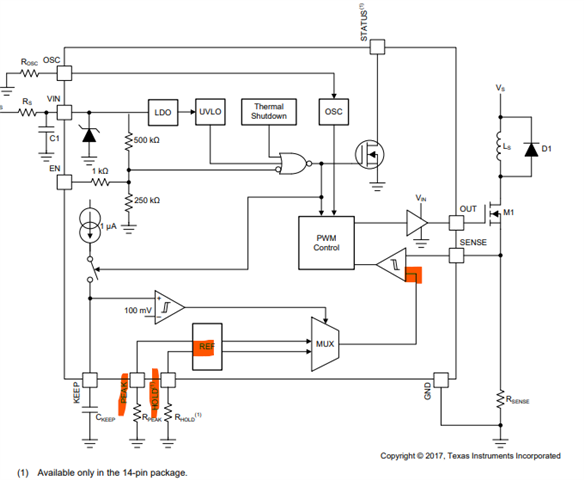

* If Vsense is smaller than Vref, a high will be generated at

* OUT pin.

* When Vsense is greater than Vrefs, OUT pin will generate a * * 10% duty cycle signal

What is wrong? How to fix it?

Thanks

antonio