Hi,

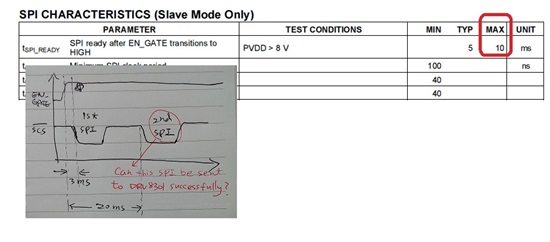

Just like to double confirm one thing for DRV8301 SPI. Please refer to the attached picture. Based on the datasheet, MCU cannot send any SPI command to DRV8301 successfully if T_SPI_RAEDY > 10 ms. So the 2nd SPI cannot be sent to DRV8301 successfully. Is it true ??

Thanks for advice.