Hello Friends,

I am a newbie.

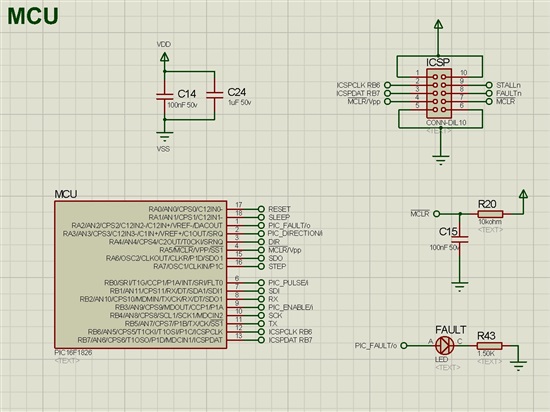

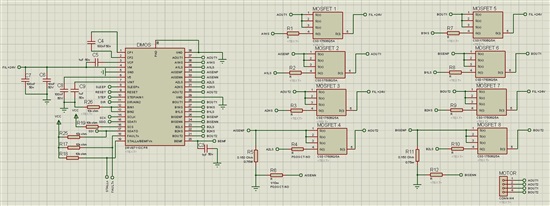

I designed a motor driver card, include a mcu and drv8711.

I am trying to programme drv8711 with SPI.

I only put a pull-up resistor to SCS pin of DRV8711 and not connect SCS pin to MCU.

I thought, it is enough to pull SCS pin high in order to execute SPI communication.

Now ı cant programme the driver.

I want to know, is this a problem (never apply low logic to SCS pin)?

Thank You!