Hello,

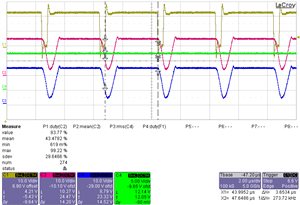

I'm using the DRV8332 to drive a BLDC motor using non-complimentary control. We PWM the driving phase and hold the other phase low. This works well most of the time but when the duty cycle begins to increase due to motor loading we see a state in which the high side is still PWM-ing however the other phases are in high impedance. It seems as if the low side FET is not on therefore the current stops and the motor stalls. Here is a plot of the phase outputs during a stall.

C1= Phase A, C2= Phase B, C3= Phase C, C4= 12V supply for GVDD.

During this conditions the FAULT line never goes low and the 12V supply is solid. The OC_ADJ resistor is 20K and is set for CBC current limit. The datasheet says " If you prefer PWM switching one channel but hold low side FET of the other channel on (and third channel in Hi-Z) for 2-quadrant mode, OT latching shutdown mode is recommended to prevent the channel with low side FET on stuck in Hi-Z during OC event in CBC mode."

The motor current doesn't seem high enough to trigger the current limiting feature but the low side FET stuck in HI-Z seems to be what I'm seeing. Can you explain what is happening and what I can do about it?

Regards,

Mike