hi, I am doing a BLDC motor driver design using DRV8301, and my circuit is similar to Boostxl-drv8301 kit except the FET used. Here is schematic and PCB file:

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/38/stpmtc001v03_2D00_gerber_2D00_150910.7z

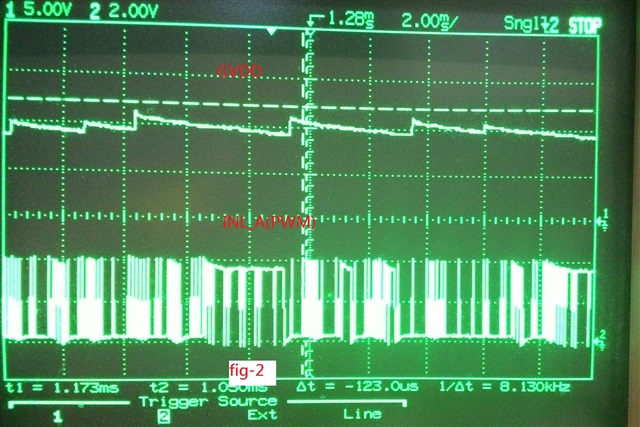

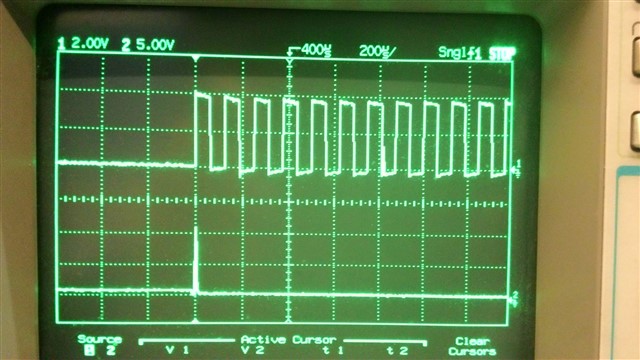

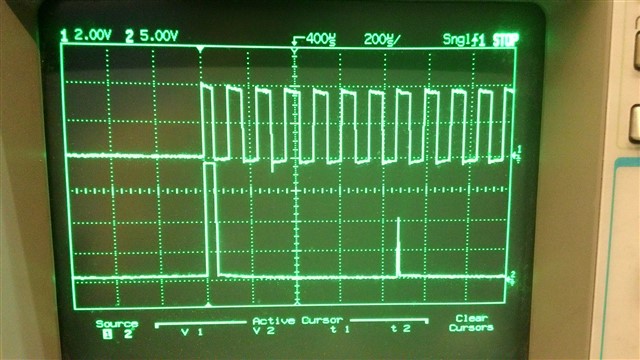

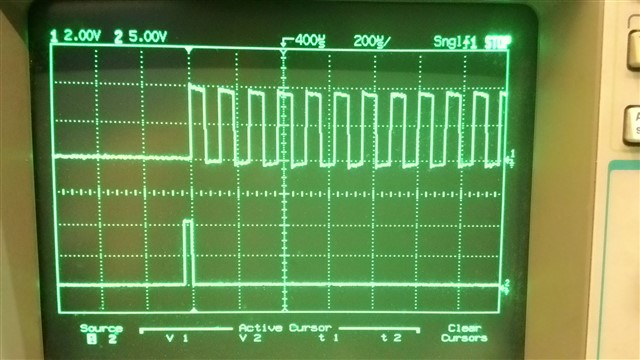

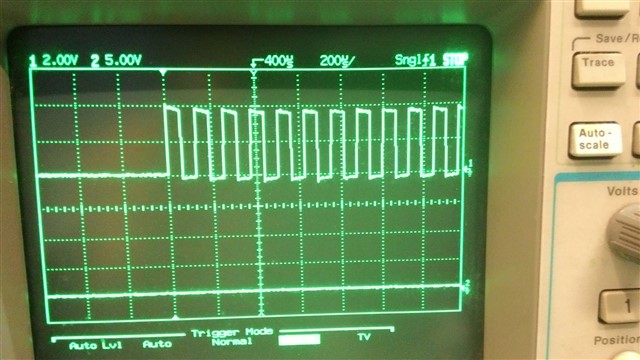

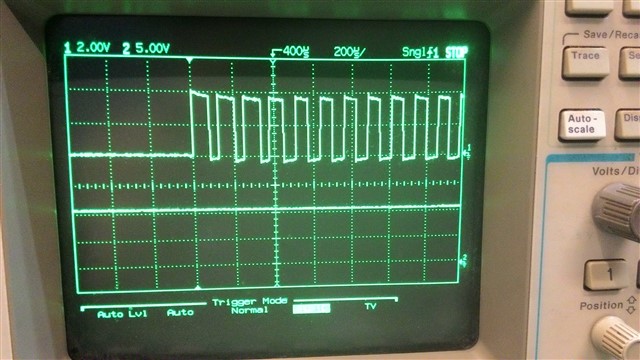

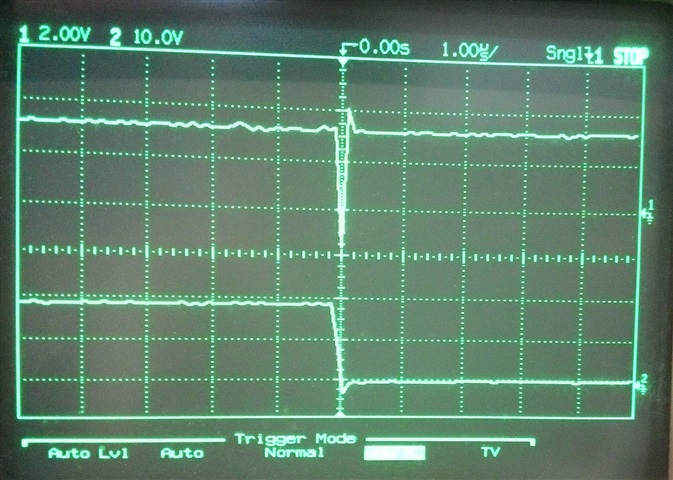

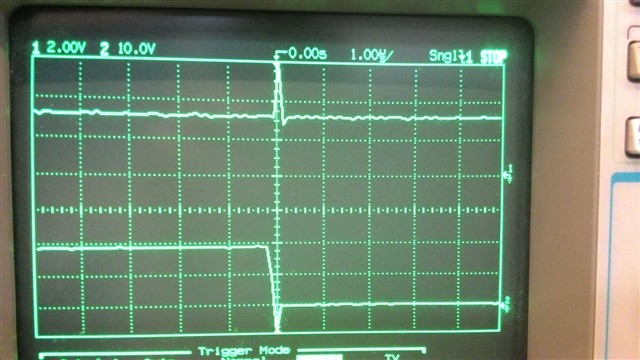

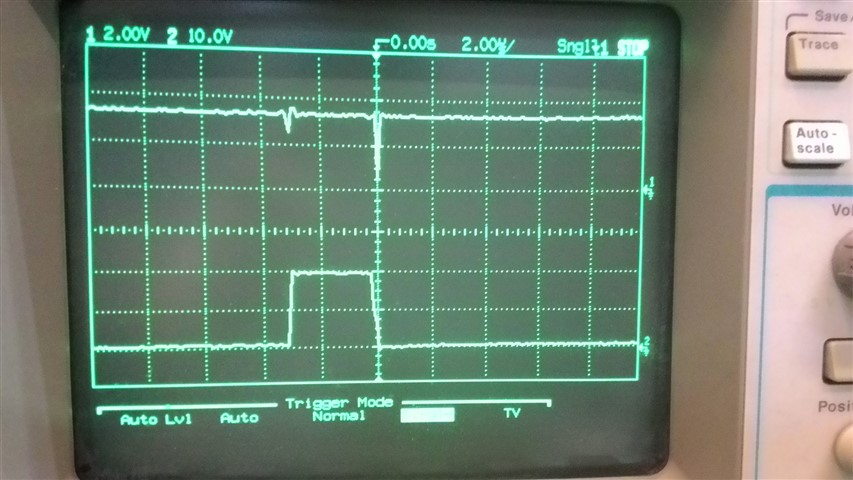

But when I use TMS320f287 to control it, the gate driver signals did work properly. And I have compared to the proper worked kit, I think it's caused by charge pump problems. The charge pump and the GVDD wave form is below:

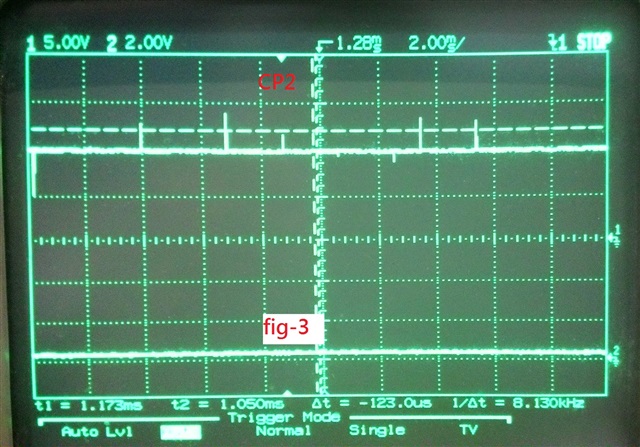

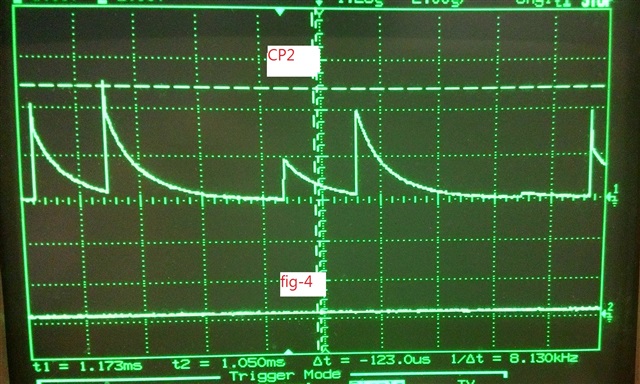

The above wave form are taken from the Drv8301 GVDD, CP2, INL_A(PWM) pins. Before the PWM signal enables, the VGDD is about 8V, and CP2 is biased at GVDD with some pulse as in fig-1, fig-3. And when PWN is enabled, the GVDD has a lot noise as in fig-2, and the CP2 can not be biased at GVDD as I compared to the working Boostxl-drv8301 demo kit.

I thoght it was caused by the PWM frequency and high Qg of FETs, I have lower down the PWM frequency to 8Khz and use the low Qg EKI06108(Gg 36nC,  ).

).

But the gate driver signals still is not working. We have made several boards, some boards can work good but for just a few seconds then the waveform is bad again. Is there any suggestions?