I'm observing fault conditions I don't understand.

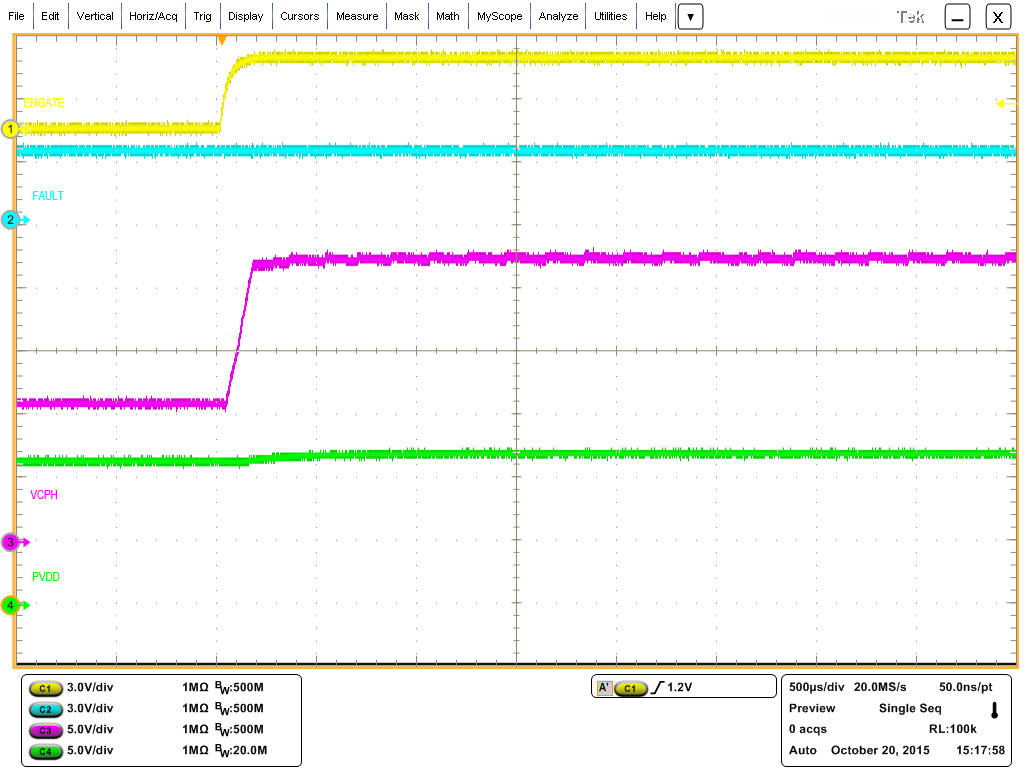

On powerup, after chip is configured, I will see a 'warning' condition (fault line toggles), which is cleared by reading register 1, the status register. The status code is 0x10, which indicates 'charge pump undervoltage'.

By reading register 1 I clear the warning (/FLT is high).

As I continue my startup code, I eventually run the code that enables the chip. As soon as I enable the chip, I get into another 'warning' condition (fault line toggles).

This time, however, when I read the status register I read 0, indicating no warnings/faults, AND the 'warning' does NOT clear.

So, it acts like I have a warning that the status register does not report. ???

I have set up register 9 with WD_EN = 0.

This seems to have something to do with enabling the chip. Why does that matter?