Hi,

We're using a DRV8303 with the overcurrent protection in latched shutdown mode. If we reset the fault condition (either via SPI or the quick pulse on EN_GATE) is there any additional delay for detecting subsequent overcurrent events on the same (or other) half-bridge?

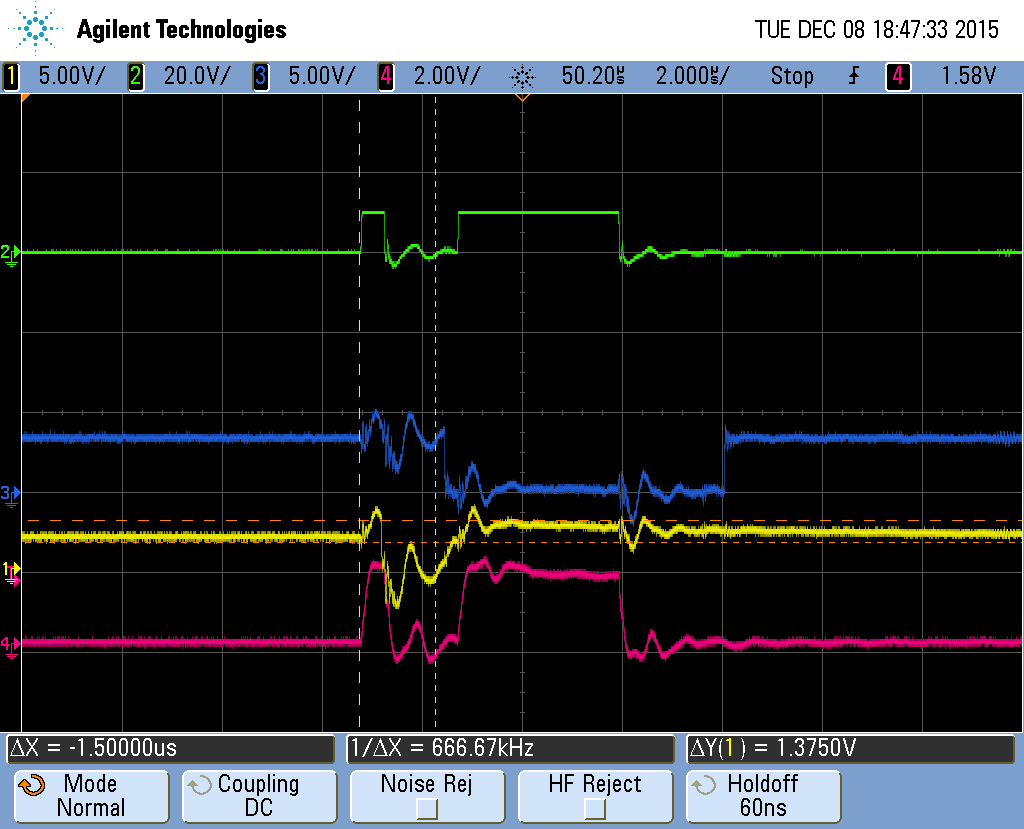

While we haven't exhausted other potential causes, we are seeing behavior which suggests an additional overcurrent event following a reset receives a delayed response and would like to rule this out as a contributing factor.

Thanks,

-Barrett