Dear all,

I use DRV8305 to control brush-less motor.

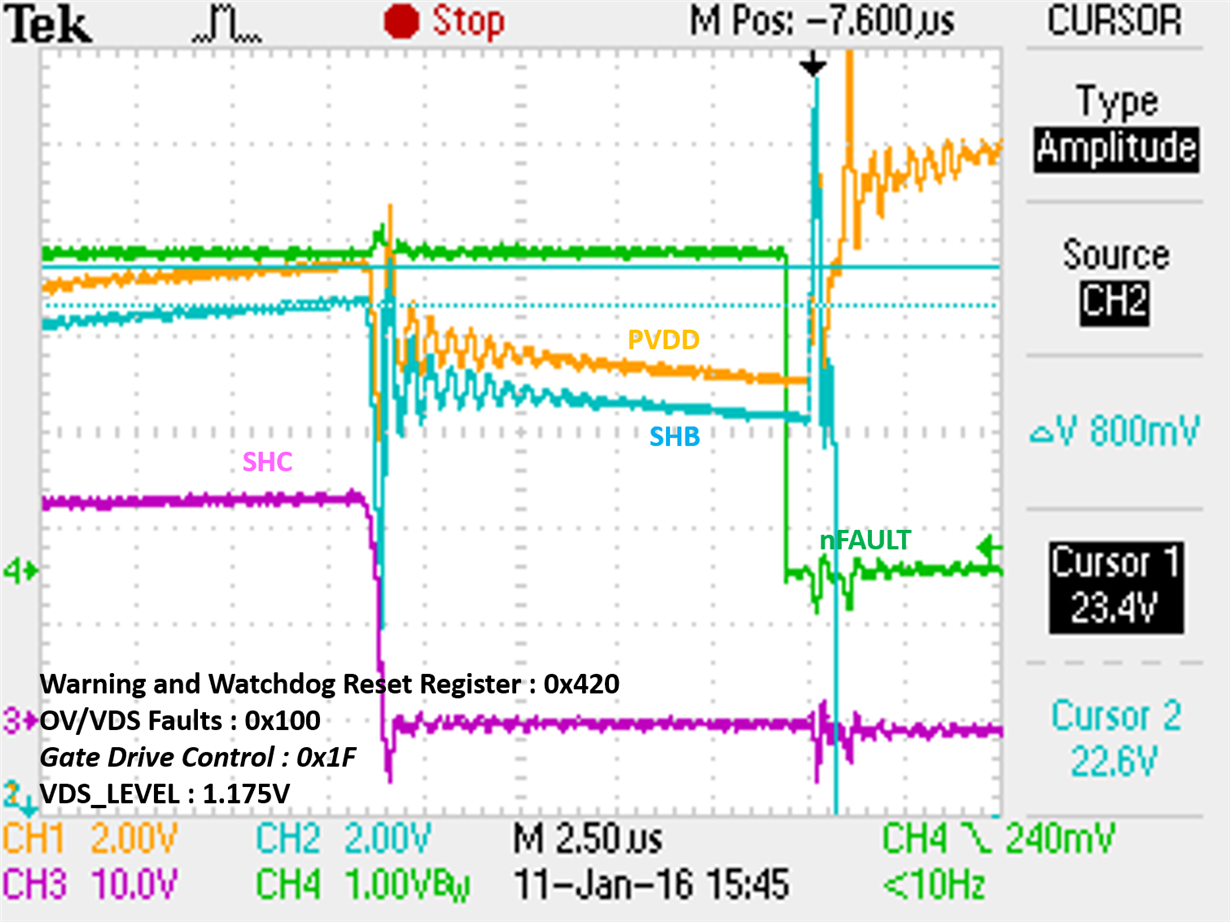

When the motor speed is controlled to be down drastically in order motor to be stopped, VDS monitor fault occurs.

Motor speed is 1200rpm before I start motor speed down.

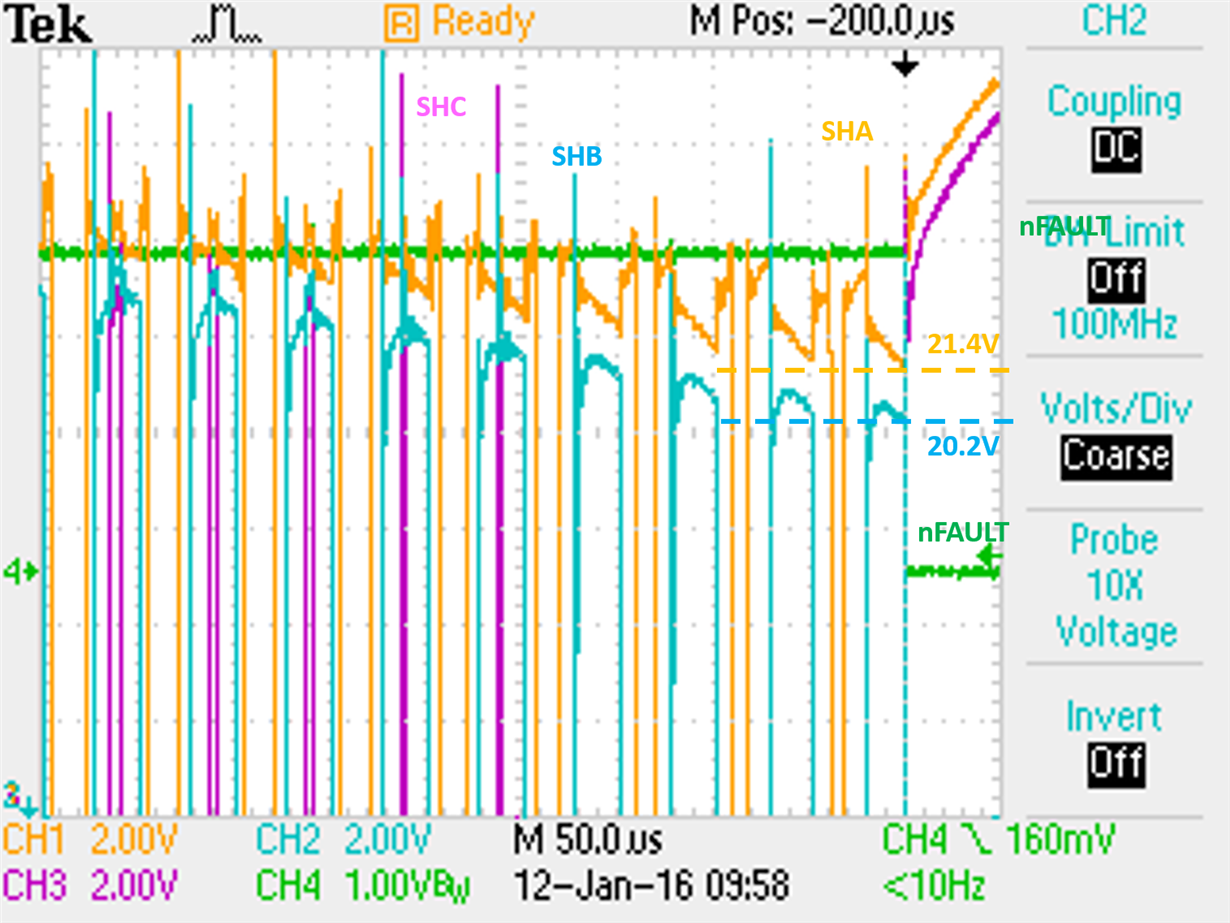

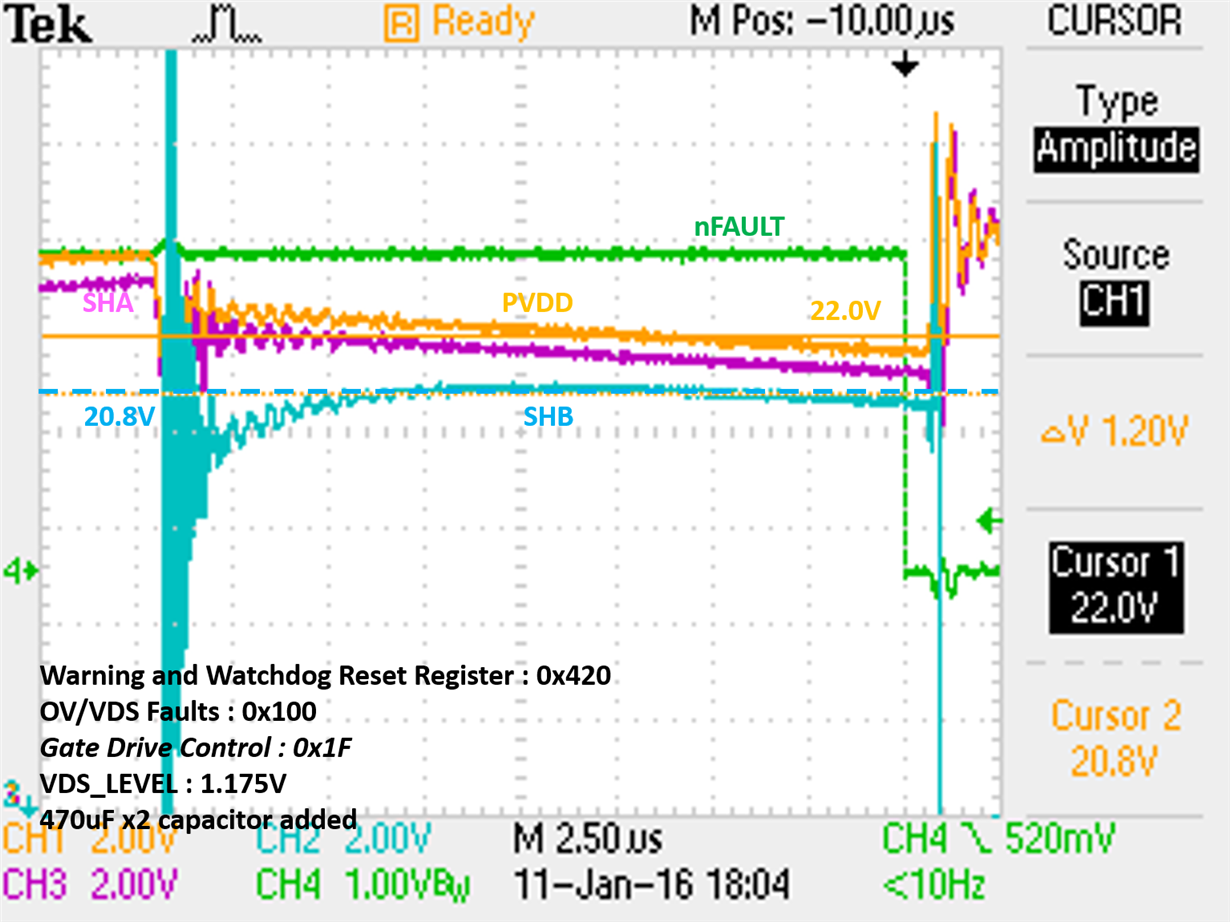

VDS monitor fault for high side FET (A, B or C) occurs with the following waveform.

According to the above waveform, PVDD drops and so two 470uF capacitors are added (total four 470uF capacitors are used now.)

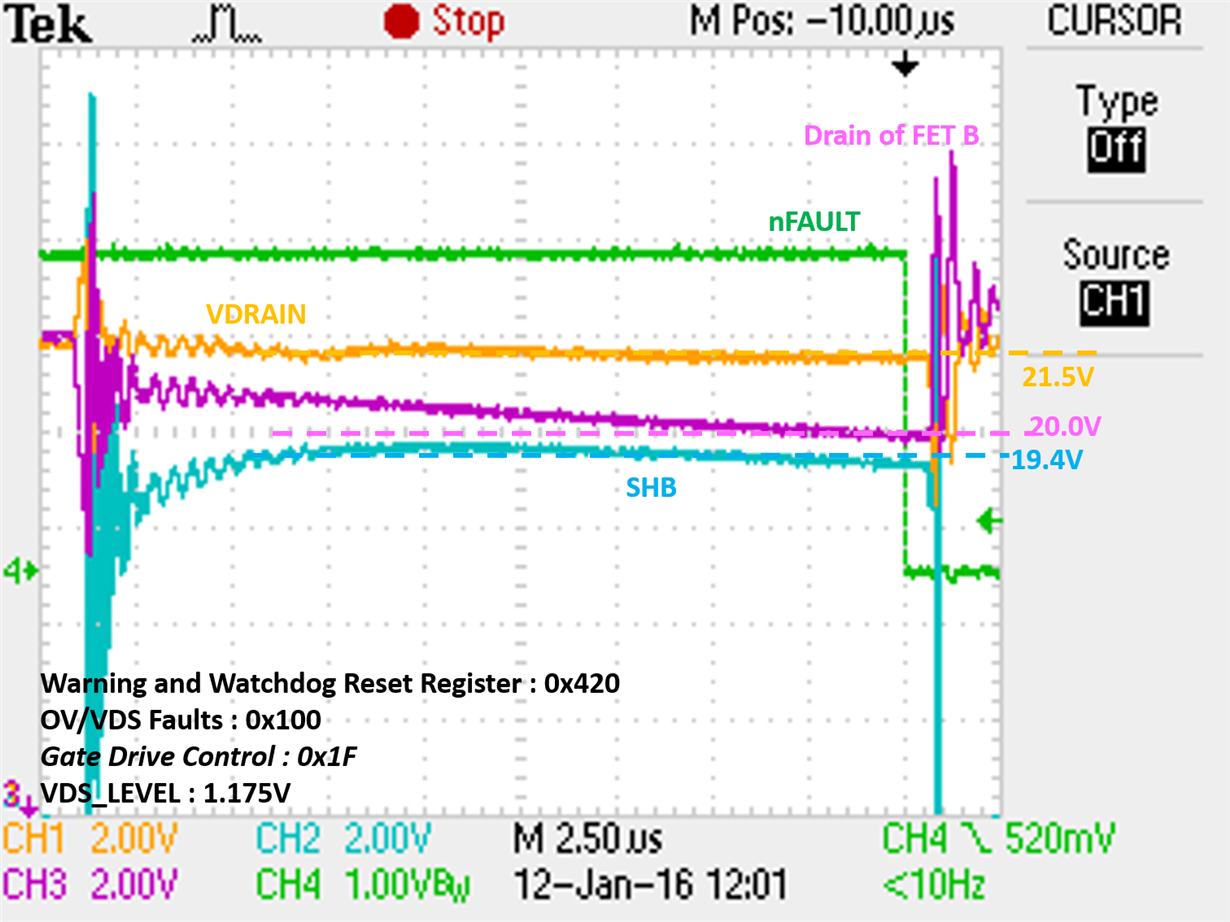

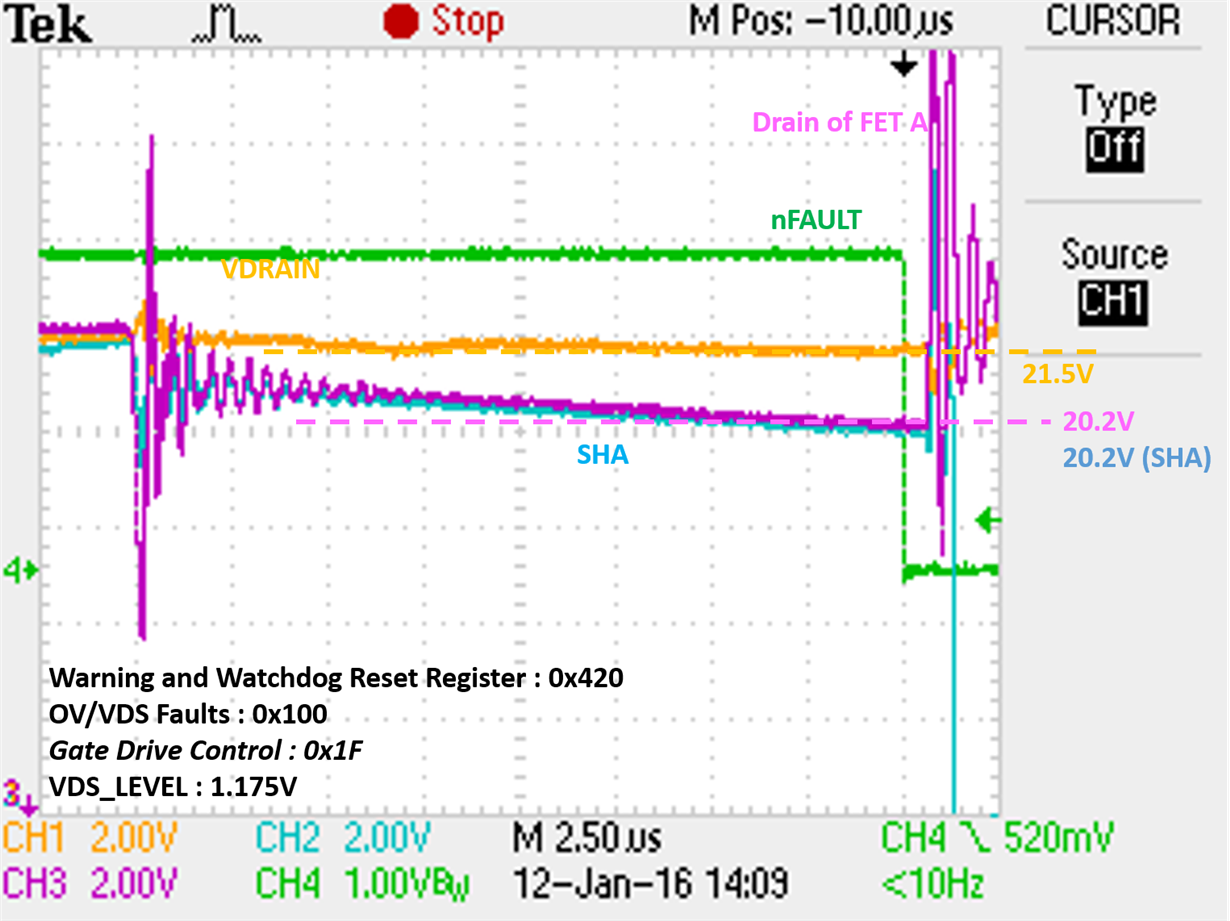

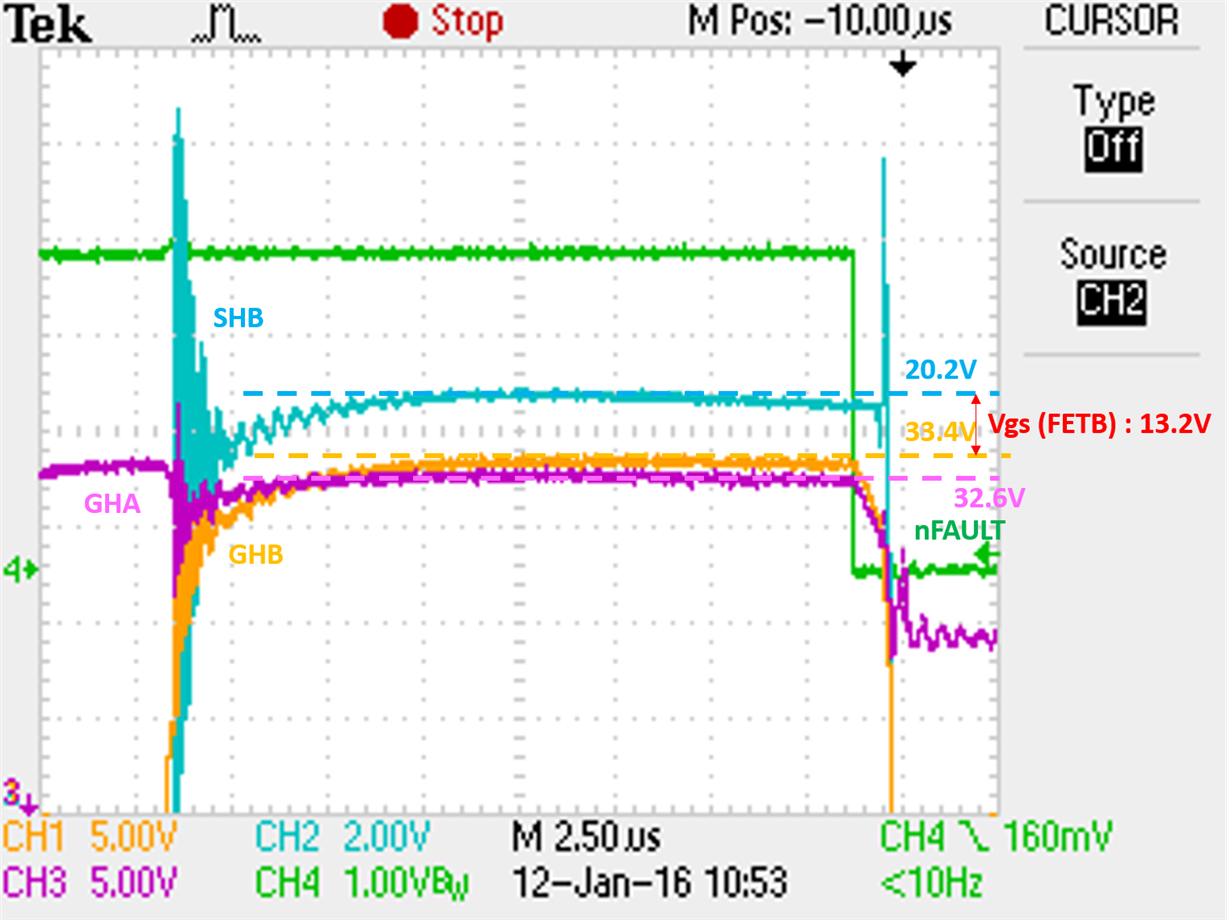

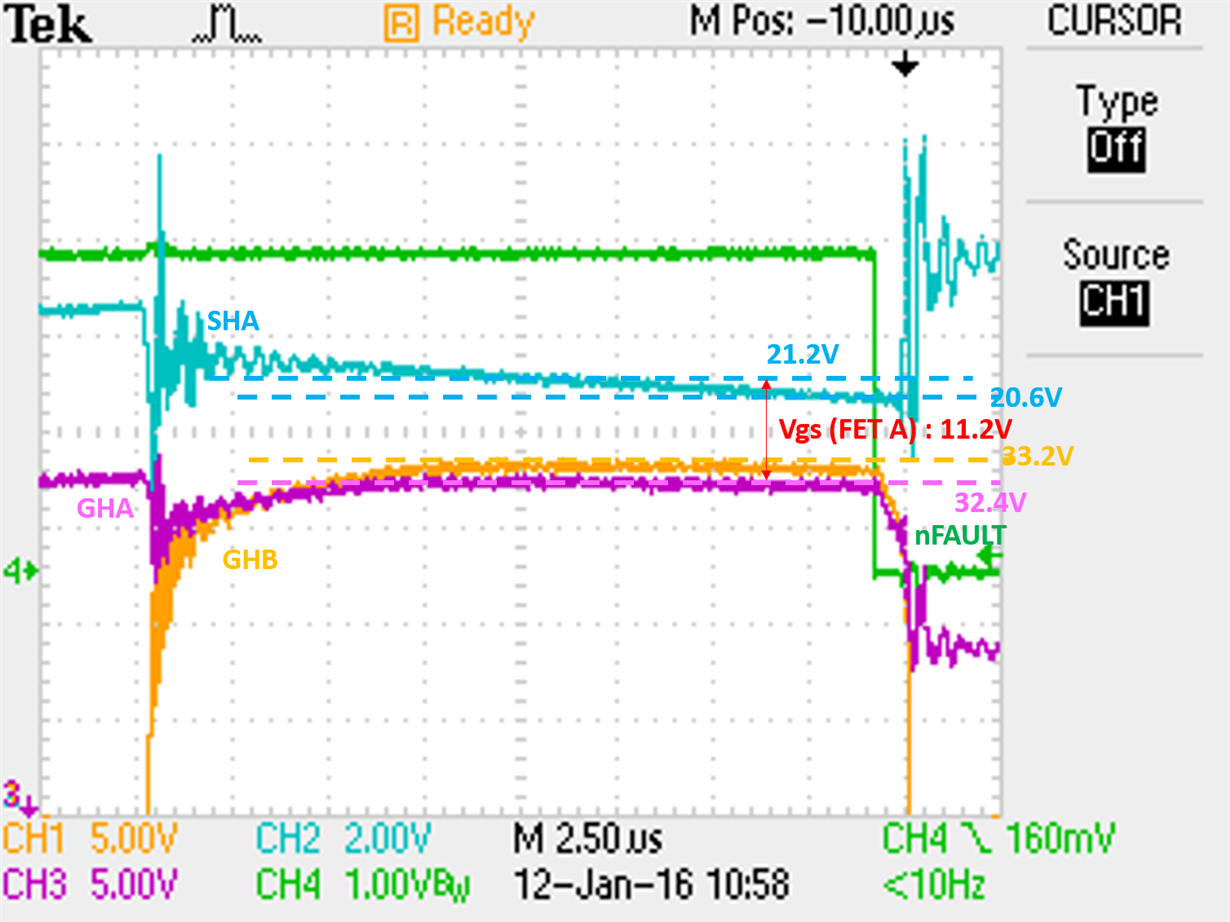

In the result, rate of VDS monitor fault is decreased but VDS monitor fault for only high side FET B sometimes occurs with the following waveform.

(My question)

1. Do you have any idea why FET B VDS is so high and VFS monitor fault for high side FET B occurs?

2. Could you tell me how to reduce VDS? (For example, adjusting slew rate prameters?)

I think VDS_LEVEL 1.175V is still so high for my FET because the FET Ron is small(1.4mOhm) but VDS monitor fault occurs.

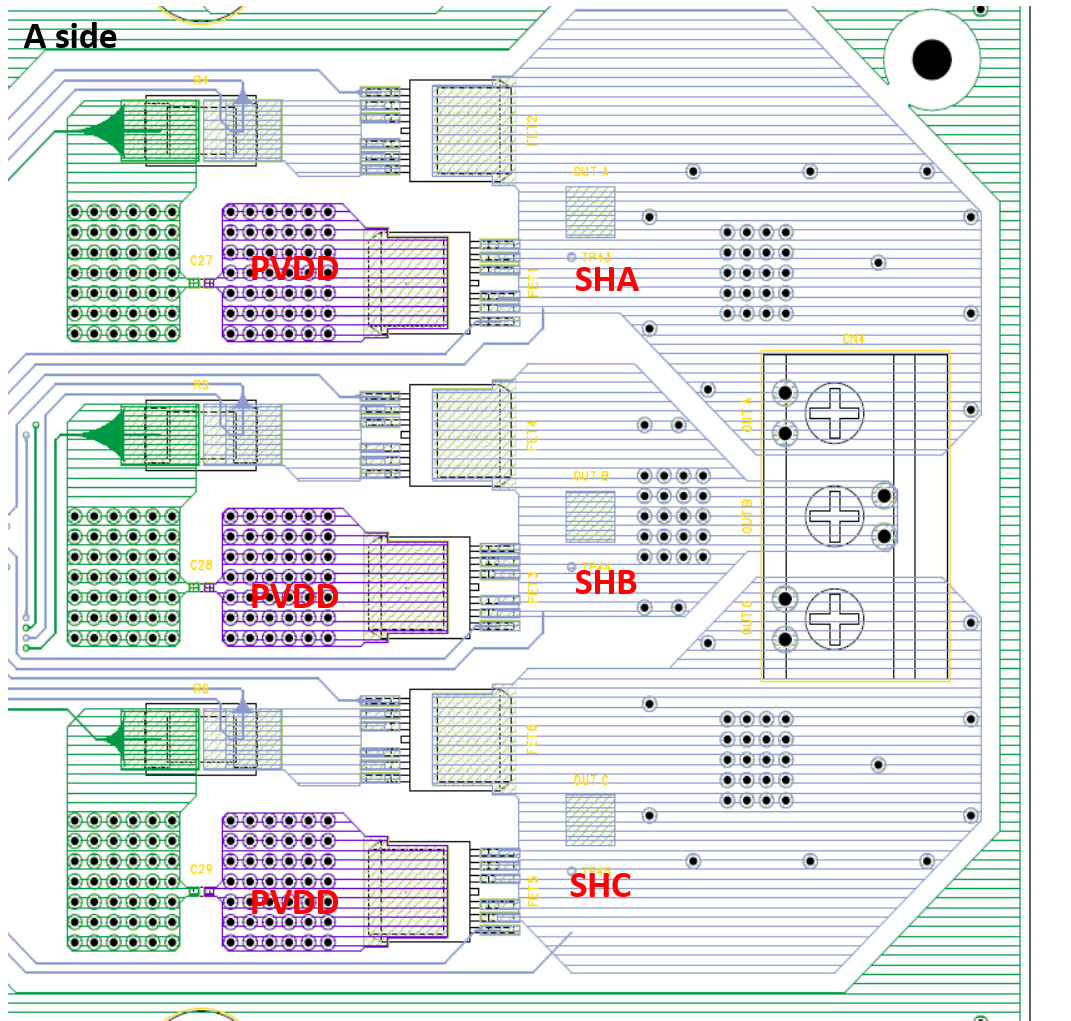

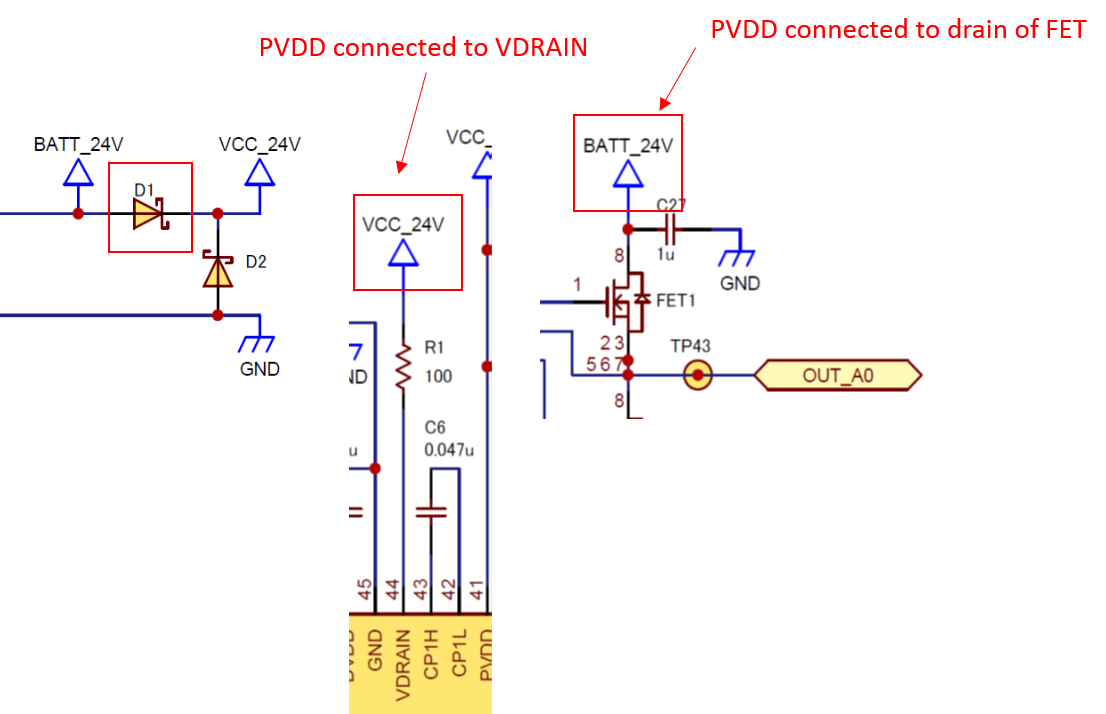

Here is the setting and my PCB information.

[Control registers setting]

HS Gate Driver Control: 0x366

LS Gate Driver Control: 0x377

Gate Drive Control: 0x1F

Shunt Amplifier Control: 0x1A

and other registers are default.

[external components]

external FET Ron: 1.4mOhm

shunt resistors : 2mOhm